Chiplets are hot now as a way to extend Moore’s Law, dividing functionality across multiple die within a single package. It’s no longer practical to jam all functionality onto a single die in the very latest processes, exceeding reticle limits in some cases and in others straining cost/yield. This is not an academic concern. Already… Read More

Tag: CXL

Stop-For-Top IP Model to Replace One-Stop-Shop by 2025

…and support the creation of successful Chiplet business

The One-Stop-Shop model has allowed IP vendors of the 2000’s to create a successful IP business, mostly driven by consumer application, smartphone or Set-Top-Box. The industry has dramatically changed, and in 2020 is now driven by data-centric application (datacenter,… Read More

Identity and Data Encryption for PCIe and CXL Security

Privacy and security have always been a concern when it comes to computing. In prior decades for most people this meant protecting passwords and locking your computer. However, today more and more users are storing sensitive data in the cloud, where it needs to be protected at rest and while in motion. In a Synopsys webinar Dana Neustadter,… Read More

Avery Levels Up, Starting with CXL

Let me acknowledge up front that Avery isn’t the most visible EDA company around. If you know of them, you probably know their X-propagation simulator. Widely respected and used, satisfying a specialized need. They have also been quietly building over the years a stable of VIPs and happy customers, with a special focus on VIPs for… Read More

Using IP Interfaces to Reduce HPC Latency and Accelerate the Cloud

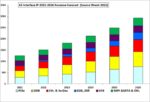

IDC has forecasted that over the next five years, the Global Datasphere — the amount of data that’s created, transferred over the network and stored each year — will increase by over 3X to 175 zettabytes (Figure 1). Much of this is driven by the Internet of Things (IoT), video applications (including video streaming,… Read More

PLDA is at the Leading Edge with Advances in Both PCIe 5.0 and CXL

There are significant advances in communication protocols happening all around us. The Peripheral Component Interconnect Express (PCIe) Gen 5 standard is delivering the needed device-to-device performance to support artificial intelligence and machine learning applications as well as cloud-based workloads. The rapidly… Read More

PLDA Brings Flexible Support for Compute Express Link (CXL) to SoC and FPGA Designers

A few months ago, I posted a piece about PLDA expanding its support for two emerging protocol standards: CXL™ and Gen-Z™. The Compute Express Link (CXL) specification defines a set of three protocols that run on top of the PCIe PHY layer. The current revision of the CXL (2.0) specification runs with the PCIe 5.0 PHY layer at a maximum… Read More

Verifying PCIe 5.0 with PLDA, Avery and Aldec

Mike Gianfagna, a fellow SemiWiki blogger and a one-time colleague at Atrenta shared a useful piece of marketing advice. If your company is not the biggest fish in the pond and you want to appear more significant, team up with other companies to put on an event, say a webinar. Pick your partners so that you can jointly offer a larger,… Read More

Verification IP Coverage

I am pleased to introduce Truechip to the SemiWiki community. Truechip is a leader in the IP Verification – Design and Verification solutions market, one of the fastest growing market segments we track. Truechip has been serving customers for more than 10 years specialization in VIP integration, customization and SOC Verification.… Read More

PLDA – Delivering Quality IP with a Solid Verification Process and an Extensive Ecosystem

For those who design advanced and complex SoCs, the term “off-the-shelf IP” can be elusive. While this approach works for a wide range of IP titles, the pressure for maximum performance or minimum power can lead to custom-tailoring requirements for the IP.

PLDA has seen these requirements for the class of complex, high-performance… Read More