Machine learning (ML) is already making its way into EDA tools and flows, but the majority of announcements have been around implementation, especially in guiding toward improved timing and area. This is a pretty obvious place to start; ML is in one sense an optimization technique, trained on prior examples, which should be able… Read More

Tag: capacity

Could China Take the Lead in Installed 300mm Capacity?

China buys more than half of the semiconductors manufactured in the world and yet only produces less the 10% of their own demand. Recently there have been a lot of announcements out of China about large scale investments in semiconductor manufacturing. The Chinese government for example has announced plans to invest $161 billion… Read More

Memory War Z: Samsung spins antidote to 3D XPoint

The 2016 edition of the Flash Memory Summit produced more than the usual amount of excitement. Samsung’s response to the Intel/Micron 3D XPoint challenge arrived in new slideware, indicating the war for next-generation SSDs is just starting. Who has the advantage?

We’d all like to think this is about creating a breakthrough technology,… Read More

Yelling fire in a crowded chip factory

Semiconductor market forecasts for 2016 are all over the place. Jim Handy and Tom Starnes floated a report in January looking for 10% growth. Jim Feldhan at Semico turned outright negative at -0.3% just a couple weeks ago. Tossing out the high and low scores, analysts tracked by GSA range from 0.3% to 7.0% in March updates. What’s … Read More

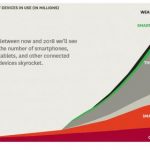

Meeting Demand as Fab Capacity is Stretched Again

Global semiconductor production capacity and its utilization level are key elements of the technology economy. During a panel at DAC in June Mentor Graphics posited that we are entering into a period where leading edge processes will be in high demand and also older nodes are seeing increasing demand due to Internet of Things designs… Read More

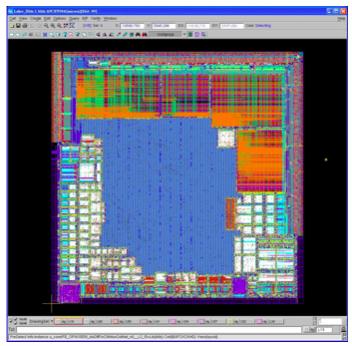

Blitz, blazing fast layout

One of the challenges with today’s SoCs is that chip-finishing, putting the final touches to the SoC working at the chip level, stresses layout editors to the limit. Either they run out of capacity to load the entire chip, or they can handle the entire chip but everything is like wading through molasses, it takes an awfully … Read More