Most IC engineers learn best by hands-on experience when another more experienced person can show us what to do. If you cannot find that experienced person, then the next best thing is a video from an expert. I was surprised to find out that video was so important today that the #2 most viewed web site on the Internet was www.youtube.com… Read More

Tag: calibre

ESD at TSMC: IP Providers Will Need to Use Mentor to Check

I met with Tom Quan of TSMC and Michael Beuler-Garcia of Mentor last week. Weirdly, Mentor’s newish buildings are the old Avant! buildings where I worked for a few weeks after selling Compass Design Automation to them. Odd sort of déja vu. Historically, TSMC has operated with EDA companies in a fairly structured way: TSMC … Read More

An easier way to deal with design rule waivers (video)

At advanced nodes, design rules are necessarily more complex and restrictive. Although most of the time you can find a way to live with them, sometimes it’s necessary to seek a waiver from the foundry for a particular design feature. This involves documenting the feature, the design rules in question and the conditions under which… Read More

Real Time Concurrent Layout Editing – It’s Possible

Layout editing is a complex task, traditionally done manually by designers, and the layout design productivity largely depends on the designer’s skills and expertise. However, a good tool with features for ease of design is a must. Layout productivity has been an area of focus and various features are constantly being added in… Read More

Robust Design <- Robust Flow <- Robust Tools

I could have written the sequence of the title in reverse order, but no, design is the one which initiates the need of a particular flow and the flow needs support of EDA tools to satisfy that need. It’s okay if the design is small; some manual procedures and workarounds/scripts may be able to perform certain jobs. However, as the design… Read More

Best Practices for Using DRC, LVS and Parasitic Extraction – on YouTube

EDA companies produce a wealth of content to help IC engineers get the best out of their tools through several means:

- Reference Manuals

- User Guides

- Tutorials

- Workshops

- Seminars

- Training Classes

- Phone Support

- AE visits

Calibre Update at DAC

Mentor Graphics throws a very nice dinner party at DAC each year for journalists, bloggers and top customers, so this year I spoke with Michael Buehler-Garcia about what’s new with Calibre.

Michael Buehler-Garcia, Mentor Graphics

… Read More

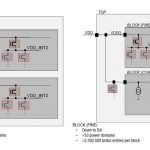

Robust Reliability Verification: Beyond Traditional Tools and Techniques

Robust Reliability Verification: Beyond Traditional Tools

by Matthew Hogan, Mentor Graphics

At all process nodes, countless hours are diligently expended to ensure that our integrated circuit (IC) designs will function in the way we intended, can be manufactured with satisfactory yields, and are delivered in a timely fashion… Read More

Bats about DAC!

DAC 2013 is closing in fast now…and if you haven’t made your plans for what you want to see and do, you’d better get going! Of course, I’m happy to help you out with a few suggestions…starting with that most important objective—conference swag. Stop by the Mentor Graphics booth (#2046, for those of you who actually look at your floor… Read More

Mentor U2U, Not Your Father’s User Conference

I talked to Michael Buehler-Garcia about the changes Mentor is making to U2U, their user conference. It is in San Jose on April 25th at the DoubleTree.

Firstly, there are 3 great keynotes, two of whom I’ve seen speak before and can unreservedly recommend. Unfortunately I’m traveling that week and won’t be able… Read More