I finished reading Don Dingee and Dan Nenni’s book, Mobile Unleashed, the Origin and Evolution of ARM Processors in Our Devices. I guess by way of disclosure I should say that Don and Dan both blogged with me here on SemiWiki for several years before I joined Cadence, and Dan’s last book Fabless was co-authored with me… Read More

Tag: cadence

The Most Important Point You May Have Missed at CDNLive 2016!

This was the best keynote lineup I can remember at a user group meeting. All four speakers are visionaries but from very different perspectives. The video of the event will be up later this month but from my first count the word “System(s)” was mentioned 32 times and the underlying message will transform the semiconductor industry… Read More

Cadence is again the best EDA company to work for!

We wrote about the history of Cadence in preparation for our book “Fabless: The Transformation of the Semiconductor Industry” in 2012. EDA played a key role in enabling the fabless semiconductor revolution and Cadence was right there at the beginning. Famed EETimes editor Richard Goering helped us with the book and the Cadence… Read More

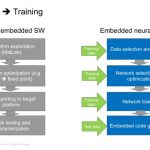

Neural Networks Ready for Embedded Platforms

If you are not yet familiar with the term Convolutional Neural Networks, or CNN for short, you are certainly bound to become in the year ahead. Using Artificial Intelligence in the form of CNN is on the verge of replacing a large number of computing tasks, especially those involving recognizing things such as sounds, shapes, objects,… Read More

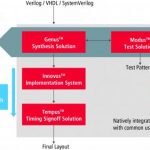

Cadence Adds New Dimension to SoC Test Solution

It requires lateral thinking in bringing new innovation into conventional solutions to age-old hard problems. While the core logic design has evolved adding multiple functionalities onto a chip, now called SoC, the structural composition of DFT (Design for Testability) has remained more or less same based on XOR-based compression… Read More

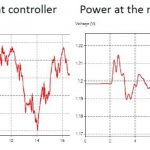

DesignCon 2016 — signal integrity must be power-aware!

DesignCon is a unique conference — its tagline is “Where the Chip meets the Board”. Held each January in Santa Clara, the conference showcases a wealth of new technologies for advanced packaging, printed circuit board fabrication, connectors, cables, and related analysis equipment (e.g, BERT, VNA, scopes). Of specific… Read More

5nm Chips? Yes, but When?

For any invention, technical proof of concept or prototyping happens years ahead of the invention being infused into actual products. When we talk about 5nm chip manufacturing, a test chip was already prototyped in last October, thanks to Cadence and Imec. Details about this chip can be found in a blog at Semiwiki (link is given … Read More

EDA and the Big Short!

A funny thing happened while I was reading “The Big Short: Inside the Doomsday Machine”. The book explains the subprime mortgage crisis in painful detail by profiling several key players who predicted and profited from the bubble pop. As a home owner and faux slumlord I had a front row seat to this horror show so it was an interesting… Read More

Semiconductors Future Hinges on a Single Pillar

A unique phenomenon has started manifesting itself under the slew of mergers and acquisitions this year in the semiconductor landscape. This phenomenon is bound to intensify in the near future and would positions itself as a key factor for the future of the semiconductor industry. The winners and losers in the game would be determined… Read More

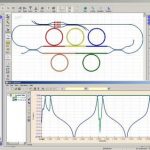

The “Era of the Photon” is here!

The 50 year anniversary of the publication of Moore’s Law was recently celebrated, highlighting the tremendous advances in the Microelectronics Eraof the period in human history known as the Information Age. However, the technical and economic challenges currently faced by the microelectronics industry are bringing into… Read More