In the EDA space, nothing seems to be more fragmented in-term of solutions than in the Design Verification (DV) ecosystem. This was my apparent impression from attending the four panel sessions plus numerous paper presentations given during DVCon 2018 held in San Jose. Both key management and technical leads from DV users community… Read More

Tag: cadence

EDA and Semiconductor — Is There Growth In The Ecosystem?

The semiconductor industry has gone through several major transitions driven by different dynamics such as shift in business models (fab-centric to fab-less), product segmentation (system design house, IP developers) and end market applications (PC to cloud; and recently, to both automotive and Internet of Things — IOT’s,… Read More

Students Should Attend DAC in SFO

On LinkedIn I have some 2,116 connections and many of those are students looking to enter the field of EDA, IP or semiconductor design. What a wonderful opportunity these students have by attending the 55th annual DAC in San Francisco this summer from June 24-28. Technical sessions, keynote speeches, exhibitors, networking, … Read More

PCB Design in the Cloud

I remember meeting John Durbetaki at Intel where we both worked in 1980, it was an exciting time and something called the Personal Computer had just been introduced by companies like Commodore, Apple and Radio Shack (yes, Radio Shack). IBM was rather late to the party with their PC in 1981, however when IBM entered the market then … Read More

IPC-2581: The Standard for PCB Data Exchange

The motivations to establish an industry standard data format are varied:

[LIST=1]

- solidify a “de facto” standard, transitioning its evolution and support from a single company to an industry consortium;

- aggregate disparate sources of design and manufacturing data into a single representation, with documented semantics;

Data Security – Why It Might Matter to Design and EDA

According to the Economist, “The world’s most valuable resource is no longer oil, but data”. Is this the case?Data is the by-product ofmany aspects of recent technology dynamics and is becoming the currency of today’s digital economy. All categories in Gartner’s Top10 Strategic Technology Trends for 2018 (Figure… Read More

Machine Learning And Design Into 2018 – A Quick Recap

How could we differentiate between deep learning and machine learning as there are many ways of describing them? A simple definition of these software terms can be found here. Let’s look into Artificial Intelligence (AI), which was coined back in 1956. The term AI can be defined as human intelligence exhibited by machines.… Read More

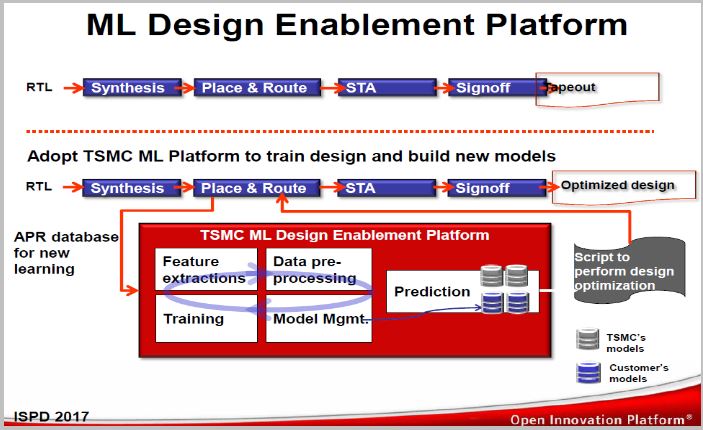

TSMC EDA 2.0 With Machine Learning: Are We There Yet ?

Recently we have been swamped by news of Artificial Intelligence applications in hardware and software by the increased adoption of Machine Learning (ML) and the shift of electronic industry towards IoT and automobiles. While plenty of discussions have covered the progress of embedded intelligence in product roll-outs, an… Read More

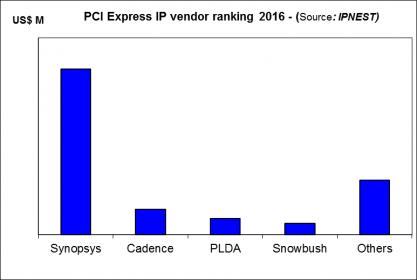

The Interface IP Market has Grown to $530 Million!

According with IPnest, the Interface IP market, including USB, PCI Express, (LP)DDRn, HDMI, MIPI and Ethernet IP segments, has reached $532 million in 2016, growing from $472 million in 2015. This is an impressive 13% Year-over-Year growth rate, and 12% CAGR since 2012!

Who integrate functions to interface a chip with others … Read More

Free eBook: Custom SoCs for IoT: Simplified

Two important trends will be discussed in this book: The disruptive nature of the Internet of Things and the use of the ASIC business model by systems companies to get into the chip business.… Read More