I attended on Monday, June 25, DAC’s Opening Day, a Cadence-sponsored Lunch panel. Ann Steffora Mutschler (Semiconductor Engineering) was the Moderator and the Panelists were Jim Hogan (Vista Ventures), David Lacey (HP Enterprise), Shigeo Oshima (Toshiba Memory Corp), Paul Cunningham (Cadence).… Read More

Tag: cadence

Liberate Trio Embraces ML and Cloud

A chain is as strong as its weakest link. This phrase resonates well in Static Timing Analysis (STA) domain, though it is about accuracy rather than durability. As timing signoff step provides the final performance readings of a design, an STA outcome is as good as its underlying components. Aside from the parasitic extraction … Read More

DAC 2018 Potpourri

The venue

Despite of being held at the new three-story Moscone West building, this year 55th DAC in San Francisco bore many similarities as compared with last year’s. Similar booth decors and floorplan positioning of the big two, Synopsys and Cadence, which were across of each other and right next to the first floor entrance –although… Read More

Legato Reliability Solution

This week Cadence introduced Legato™ Reliability Solution, intended to address increased challenges in designing high-reliability analog and mixed-signal ICs for automotive, industrial, aerospace and defense applications.… Read More

imec and Cadence on 3nm

One of the more frequent questions I get, “What is next after FinFETs?” is finally getting answered. Thankfully I am surrounded by experts in the process technology field including Scotten Jones of IC Knowledge. I am also surrounded by design enablement experts so I really am the man in the middle which brings us to a discussion between… Read More

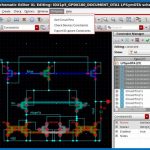

The Intention View: Disruptive Innovation for Analog Design

Intento Design builds responsive analog EDA. The ID-Xplore tool is used for analog design acceleration and technology porting at the functional level, helping companies move analog IP quickly between technology nodes and across business units. The Intention view is a simple, elegant, and powerful concept that gives the speed… Read More

Enabling A Data Driven Economy

The theme of this year CDNLive Silicon Valley keynote given by Cadence CEO, Lip-Bu Tan evolves around data and how it drives Cadence to make a transition from System Design Enablement (SDE) to Data Driven Enablement (DDE). Before elaborating further, he noted on some CDNLive conference statistics: 120 sessions, 84% done by users,… Read More

Functional Safety Methodologies for Automotive Applications

During Q&A session at San Jose GTC 2018, nVidia CEO Jen-Hsun Huang reiterated that critical functional safety, such as in autonomous vehicle, requires both the redundancy and the diversity aspects. For example, CUDA with Tensor core and GPU with DLA were both utilized. Safety is paramount to automotive applications. Any… Read More

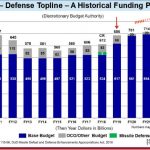

Meeting the Challenges of National Defense Strategy

In February this year, the Department of Defense (DoD) submitted a $686.1 billions budget for 2019 and published a National Defense Strategy outlining the overall spending for defense and military programs. The recently signed US $1.3 trillion spending bill included part of the funding. According to DoD Defense Budget Overview… Read More

Don’t Stand Between The Anonymous Bug and Tape-Out (Part 2 of 2)

The second panel is about system coverage and big data. Coverage metrics have been used to gauge the quality of verification efforts during development. At system level, there are still no standardized metrics to measure full coverage. The emergence of PSS, better formal verification, enhanced emulation and prototyping techniques… Read More