Two recently announced vulnerabilities in major processor platforms should remind us that bugs don’t organize themselves to appear only in domains we know how to test comprehensively. Both Meltdown and Spectre (the announced problems) are potential hardware system-level issues allowed by interactions between speculative… Read More

Tag: bernard murphy

CEVA ClearVox Simplifies Voice Pickup

Voice-based control is arguably becoming another killer app, or killer app-enabler in the very significant shifts we are seeing in automation. After a bumpy start in car feature control (for navigation, phone calls, etc) and early smartphone “intelligent” assistants, voice-based interfaces now seem to be maturing into a genuinely… Read More

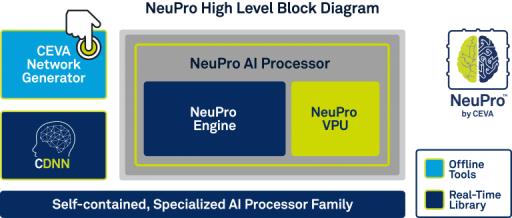

CEVA Ups the Ante for Edge-Based AI

AI is quickly becoming the new killer app and everyone is piling on board as fast as they can. But there are multiple challenges for any would-be AI entrepreneur:

- Forget about conventional software development; neural nets require a completely different infrastructure and skill-sets

- More and more of the interesting opportunity

How Deep Learning Works, Maybe

Deep learning, modeled (loosely) on the way living neurons interact, has achieved amazing success in automating recognition tasks, from recognizing images more accurately in some cases than we or even experts can, to recognizing speech and written text. The engineering behind this technology revolution continues to advance… Read More

What’s old is new again – Analog Computing

Once in a while I like to write on a fun, off-beat topic. My muse today is analog computing, a domain that some of us antiques in the industry recall with fondness, though sadly in my case without hands-on experience. Analog computers exploit the continuous nature of analog signals together with a variety of transforms to represent… Read More

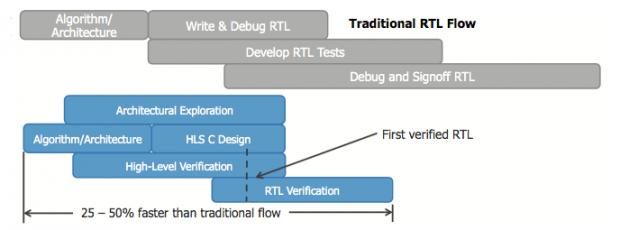

HLS Rising

No-one could accuse Badru Agarwala, GM of the Mentor/Siemens Calypto Division, of being tentative about high-level synthesis. (HLS). Then again, he and a few others around the industry have been selling this story for quite a while, apparently to a small and not always attentive audience. But times seem to be changing. I’ve written… Read More

Aldec and High-Performance Computing

Aldec continues to claim a bigger seat at the table, most recently in their attendance at SC17, the supercomputing conference hosted last month in Denver. I’m really not sure how to categorize Aldec now. EDA company seems to miss the mark by a wide margin. Prototyping company? Perhaps, though they have a much stronger focus on end-applications… Read More

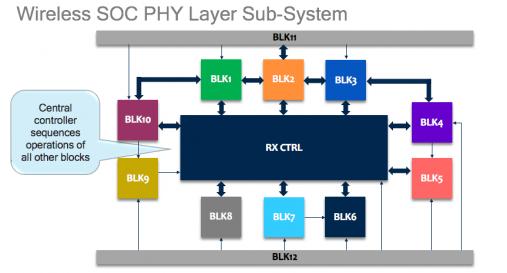

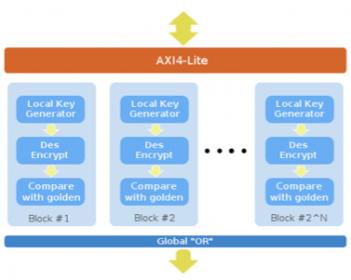

Networking and Formal Verification

I attended Oski’s latest Decoding Formal event a couple of weeks ago and again enjoyed a largely customer-centric view of the problems to which they apply formal, and their experiences in making it work for them (with Oski help of course). From an admittedly limited sample of two of these events, I find them very representative of… Read More

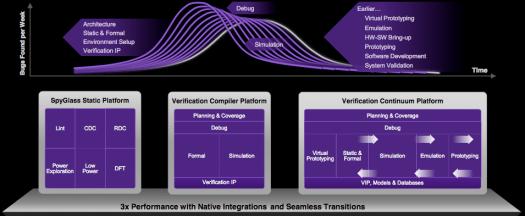

Shifting Left with Static and Formal Verification

Unless you have been living in a cave for the last several years, by now you know that “Shift Left” is a big priority in product design and delivery, and particularly in verification. Within the semiconductor industry I believe Intel coined this term as early as 2002, though it seems now to be popular throughout all forms of technology… Read More

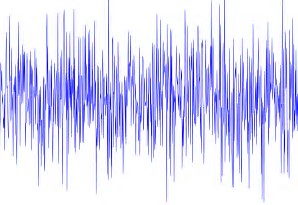

Creative Noise-Reduction in Automotive AMS

Automotive applications are one of the hottest domains today in semiconductor design. We’re bombarded daily with articles on new hybrids, electric cars, ADAS and autonomous cars, trucks and busses. All of these applications are certainly amazing, but the devices that make them work still have to deal with the same old challenges,… Read More