You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

What do you do next when you’ve already introduced an all-in-one extreme edge device, supporting AI and capable of running at ultra-low power, even harvested power? You add a software flow to support solution development and connectivity to the major clouds. For Eta Compute, their TENSAI flow.

The vision of a trillion IoT… Read More

I’m going to get to low power and RISC-V, but first I’m trying out virtual DAC this year. Seems to be working smoothly, aside from some glitches in registration. But maybe that’s just me – I switched email addresses in the middle of the process. Some sessions are live, many pre-recorded, not quite the same interactive experience… Read More

Many of us are now somewhat fluent in IoT-speak, though at times I have to wonder if I’m really up on the latest terminology. Between edge and extreme edge, fog and cloud, not to mention emerging hierarchies in radio access networks – how this all plays out is going to be an interesting game to watch. Ron Lowman, DesignWare IP Product… Read More

After we detect a bug, can we use AI to locate the fault, or at least get close? Paul Cunningham (GM of Verification at Cadence), Jim Hogan and I continue our series on novel research ideas, through a paper in software verification we find equally relevant to hardware. Feel free to comment.

The Innovation

This month’s pick is… Read More

Back in my Atrenta days (before mid-2015), we were already running into a lot of very large SoC-level designs – a billion gates or more. At those sizes, full-chip verification of any kind becomes extremely challenging. Memory demand and run-times explode, and verification costs explode also since these runs require access to … Read More

Got a great idea for a device with AI at the extreme edge? Self-contained and can run on a coin cell battery, maybe even harvested energy? Needs to fit in a space not much larger than a quarter? Eta Compute has a board for you. This comes with 2 MEMS microphones, a pressure/temperature sensor, a 6-axis MEMS accelerometer/gyroscope,… Read More

Late last year I wrote about Arm’s efforts to play a role in servers, in AWS, and particularly Arm-based supercomputing, in the Sandia Astra roadmap and in partnering with NVIDIA who are in the Oak Ridge Summit supercomputer. These steps came, at least for me, with an implicit “Good for them, playing a role on the edges of these challenging… Read More

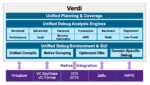

Want fast debug? Synopsys recently hosted a Webinar to show off the latest and greatest improvements to Verdi® in performance, memory demand and multi-tasking, among other areas.

Performance improvements

Taruna Reddy (PMM) and Allen Hsieh (Staff apps) presented features of the latest version, released in March – Taruna started… Read More

I don’t look at the RTL power estimation topic too often these days, so I was interested to see that ANSYS still has a very strong position in this area. Qualcomm is using PowerArtist on one of the most demanding modern applications – mobile GPU power gaming. Mobile gaming heavily loads the GPU, so any optimization in that area will … Read More

I believe I asked this question a year or two ago and answered it for the absolute bleeding edge of datacenter performance – Google TPU and the like. Those hyperscalars (Google, Amazon, Microsoft, Baidu, Alibaba, etc) who want to do on-the-fly recognition in pictures so they can tag friends in photos, do almost real-time machine… Read More