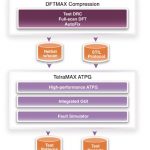

Traditionally ATPG (Automatic Test Pattern Generation) and BIST (Built-In-Self-Test) are the two approaches for testing the whole semiconductor design squeezed on an IC; ATPG requires external test equipment and test vectors to test targeted faults, BIST circuit is implemented on chip along with the functional logic of IC.… Read More

Tag: atpg

How to Assure Quality of Power and SI Verification?

As power has become one of the most important criteria in semiconductor design today, I was wondering whether there is a standard set for the power verification for an overall chip. We do have formats evolved like CPF and UPF and there are tools available to check power and signal integrity (SI), however I don’t see a standard objective… Read More

What Mentor Said at ITC

At the ITC test conference in early September, Mentor made three announcements. ITC is a big event for Mentor’s test group, and where they usually roll out their new tools and capabilities. The indefatigable Steve Pateras was captured on film describing them.

I’ve summarize Mentor’s three announcements and added… Read More

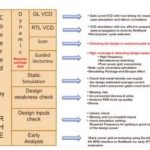

Early Test –> Less Expensive, Better Health, Faster Closure

I am talking about the health of electronic and semiconductor design, which if made sound at RTL stage, can set it right for the rest of the design cycle for faster closure and also at lesser cost. Last week was the week of ITC(International Test Conference) for the Semiconductor and EDA community. I was looking forward to what ITC… Read More

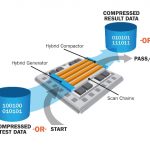

A Hybrid Test Approach – Combining ATPG and BIST

In the world of IC testability we tend to look at various approaches as independent means to an end, namely high test coverage with the minimum amount of test time, minimum area impact, minimum timing impact, and acceptable power use. Automatic Test Pattern Generation (ATPG) is a software-based approach that can be applied to any… Read More

SpyGlass: Focusing on Test

For decades we have used a model of faults in chips that assumes that a given signal is stuck-at-0 or stuck-at-1. And when I say decades, I mean it. The D-algorithm was invented at IBM in 1966, the year after Gordon Moore made a now very famous observation about the number of transistors on an integrated circuit. We know that stuck-at… Read More

Scan the horizon, P1687 takes us higher

The tech standards cycle almost always goes like this: Problems or limits develop with the existing way of doing things. Innovators attempt to engineer solutions, usually many of them. Chaos ensues when customers figure out nothing new works with anything else. Competitors sit down and agree on a specification where things work… Read More

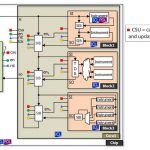

Minimize the Cost of Testing ARM® Processor-based Designs and Other Multicore SoCs

On my first job out of college as an IC design engineer I was surprised to discover that a major cost of chips was in the amount of time spent on the tester before being shipped. That is still true today, so how would you keep your tester time down, test coverage high and with a minimum number of pins when using multiple processors on a single… Read More

Testing an IC Sandwich

At a lovely, but chilly, 3DIncites awards breakfast during SEMICON West, I saw Mentor Graphics win in two of five categories (Calibre 3DSTACK was the other winner). Afterwards, I talked to Steve Pateras, the product marketing director of Mentor’s test solutions about Tessent Memory BIST, which was one of the winners. I asked Pateras… Read More

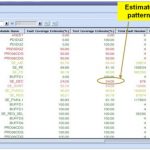

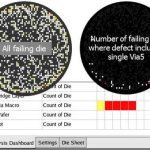

A Goldmine of Tester Data

Yesterday at SEMICON West I attended an interesting talk about how to use the masses of die test data to improve silicon yield. The speaker was Dr. Martin Keim, from Mentor Graphics.

First of all, he pointed out that with advanced process nodes (45nm, 32nm, and 28nm), and new technologies like FinFETs, we get design-sensitive defects.… Read More