Here, I am talking about reliability of chip design in the context of electrical effects, not external factors like cosmic rays. So, the electrical factors that could affect reliability of chips could be excessive power dissipation, noise, EM (Electromigration), ESD (Electrostatic Discharge), substrate noise coupling and… Read More

Tag: asic

The Funnest Bug

We all have a funnest bug we’ve been involved with. I don’t think ‘funnest’ is actually a word but when my kids used to use the word ‘funner’ I didn’t have a good argument as to why it wasn’t a word, it just seemed a word I’d never heard. In fact I have no idea what the rules are… Read More

A Brief History of VLSI Technology, part 2

VLSI’s business grew healthily but it never threw off enough cash to fund all the investment required for process technology development and capital investment for a next generation fab. They made a strategic partnership with Hitachi covering both 1um process technology and a significant investment, which meant that … Read More

A Brief History of VLSI Technology, part 1

VLSI Technology was founded in 1981 by Dan Floyd, Jack Baletto and Gunnar Wetlesen who had worked together at Signetics. The initial investments were by Hambrecht and Quist, a cross between a VC and a bank, and by Evans and Sutherland, the simulation/graphics company.

The fourth person to join the company was Doug Fairbairn. He … Read More

Full Visibility in ASIC Prototypes at DAC

ASIC prototyping from multiple vendors using FPGA boards was popular at DAC again this year in Austin, Texas. I stopped by the Tektronix booth for a few minutes to meet with Dave Orecchio to get an update.

Dave Orecchio (right), Tektronix… Read More

Missed #50DAC? See Aldec Verification Sessions Online

Aldec, Inc. is an industry-leading Electronic Design Automation (EDA) company delivering innovative design creation, simulation and verification solutions to assist in the development of complex FPGA, ASIC, SoC and embedded system designs. With an active user community of over 35,000, 50+ global partners, offices worldwide… Read More

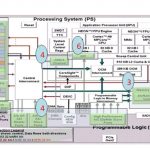

FPGAS – The New Single Board Computers?

I have always felt that FPGAs have been the red haired step child of Silicon Valley. Software weenies have hated them, they are mysterious and take too long to route. Even though they can be massively parallel and the most deterministic piece of silicon you can buy besides a million dollar ASIC, the GPU steals their glory, for now. … Read More

Webinar: Making a Simple, Structured and Efficient VHDL Testbench

Most simple testbenches have close to no structure, are terrible to modify and hopeless to understand. They often take far too much time to implement and provide close to no support when debugging potential problems. This webinar will demonstrate how to build a far better testbench with respect to all these issues – in significantly… Read More

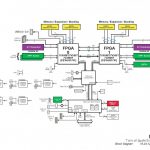

ASIC Prototyping: Dini Group and Tektronix

Collaboration in EDA is nothing new, however you may not be aware of how the Dini Group and Tektronix have worked together on an FPGA prototyping platform to address issues like debugging with full visibility across an entire multi-FPGA design. At SemiWiki we’ve blogged a couple of times so far about the new debug approach… Read More

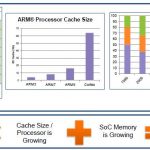

How much SRAM proportion could be integrated in SoC at 20 nm and below?

Once upon a time, ASIC designers were integrating memories in their design (using a memory compiler being part of the design tools provided by the ASIC vendor), then they had to make the memory observable, controllable… and start developing the test program for the function, not a very enthusiastic task (“AAAA” and “5555” and other… Read More