The 26th Conference on VLSI Design will be in Pune, India from January 5th to 10th at the Hyatt Regency. Details on the conference here. Registration here. I happened to be involved in the first of these conferences, which was held in Edinburgh where I was wrapping up my PhD. It was in the considerably less palatial surroundings of … Read More

Tag: ansys

Apache Power Artist Capabilities I

I sat down last week with Paul Traynar who was over from UK. He is Apache’s PowerArtist guru. The first thing we talked about was PowerArtist’s sequential power reduction capabilities.

Forward propagation of enables means that when a register is clock gated and feeds a downstream register then that register can be… Read More

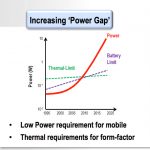

Power and Reliability Challenges

Last week I attended the Ansys/Apache seminars on “Dimensions of Electronic Design.” The two big challenges as we go down to 28nm and 20nm and below are keeping power manageable and keeping reliability up.

The big challenge with power is that we can put so much stuff on a die and clock it so fast that the power is exceeding… Read More

Apache Dimensions of Electronic Design Seminars

Coming up are ANSYS/Apache seminars on Dimensions of Electronic Design. Watch the video where Arvind Shanmugavel gives some details about why you should attend. Probably most readers are in Silicon Valley, and the seminar here is on 18th at the Hyatt (next to Santa Clara convention center).

The seminars are free to qualified attendees.… Read More

Dimensions of Electronic Design Seminars

ANSYS and Apache are putting on a new series of seminars about designing future electronic systems. These are only getting more complex, of course, cramming more and more functionality into smaller portable devices with good battery life (and not getting too hot), integrating multiple antennas into a single platform, and TSV-based… Read More

Chip Aware System Design

On Wednesday this week Ansys/Ansoft/Apache are presenting a new webinar Chip Aware System Design. It is presented by Dr Steven Gary Pytel Jr of the Ansoft part of Ansys, and Matt Elmore of the Apache subsidiary. The topics that will be covered include:

- Power Delivery Network (PDN) design requirements

- ABCD Matrix theory

- SYZ Matrix

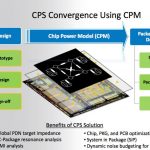

Chip-Package-System Webinar

Aveek Sarkar presented a webinar on chip-package-system (CPS) earlier this summer. One of the big challenges with low-power electronic systems is that the performance, power and price goals are mutually conflicting. It’s like the old joke about “pick any 2”. But for a real system all need to be optimized. … Read More

3D Memories

At DesignCon earlier this year, Tim Hollis of Micron gave an interesting presentation on 3D memories. For sure the first applications of true 3D chips are going to be stacks of memory die and memory on logic. The gains from high bandwidth access to the memory and the physically closer distance from memory to processor are huge.

Micron… Read More

Apache Low Power Webinars

For those of you who didn’t get to DAC you can catch up on low power issues with Apache’s series of low-power webinars taking place late in July. All webinars are at 11am Pacific Time. Full details and registration on the Apache website here.… Read More

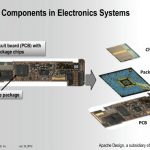

TSMC Theater Presentation: Apache

At the TSMC Theater Apache (don’t forget, now a subsidary of Ansys) talked about Emerging Challenges for Power, Signal and Reliability Verification on 3D-IC and Silicon Interposer Designs. The more I see about the costs and challenges of 20/22nm and below, the more I think that these 3D and 2.5D approaches are going to be … Read More