2015 will be remembered as the year when chip-package-system (CPS) physical co-design and electrical/thermal analysis methodologies took center stage.… Read More

Tag: ansys

EDA and the Big Short!

A funny thing happened while I was reading “The Big Short: Inside the Doomsday Machine”. The book explains the subprime mortgage crisis in painful detail by profiling several key players who predicted and profited from the bubble pop. As a home owner and faux slumlord I had a front row seat to this horror show so it was an interesting… Read More

Semiconductors Future Hinges on a Single Pillar

A unique phenomenon has started manifesting itself under the slew of mergers and acquisitions this year in the semiconductor landscape. This phenomenon is bound to intensify in the near future and would positions itself as a key factor for the future of the semiconductor industry. The winners and losers in the game would be determined… Read More

A Synergistic Chip-Package-System Analysis Methodology

Looking back, 2015 was a significant year for mergers and acquisitions in the EDA industry. The Semiwiki team maintains a chronology of major transactions here.

As I was reviewing this compendium, one of the entries that stands out is the acquisition of Apache Design Solutions by Ansys, Inc. a couple of years ago.

At that time, there… Read More

5 Verification Challenges of IoT Solved by Emulation

Software-centric Emulation environment takes the forefront in modern SoC verification. As more and more devices are IoT enabled, the SoCs have to make special provisions to factor many things including communication, power usage, and network switching, and so on. Also, the demand for an SoC (specifically for smartphone which… Read More

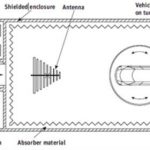

Simulating Full-System EMI for a Car in Just 28 Minutes

While there’s a lot of cool technology in modern semiconductors, it’s important to raise our sights periodically to understand how well these chips will work in the systems for which they are designed. One area driving a lot of semiconductor growth is automobile electronics. We’ve had drive-train control forever it seems, but… Read More

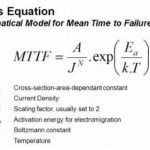

Electromigration Analysis and FinFET Self-Heating

FinFET processes provide power, performance, and area benefits over planar technologies. Yet, a vexing problem aggravated by FinFET’s is the greater local device current density, which translates to an increased concern for signal and power rail metal electromigration reliability failures. There is a critical secondary… Read More

Why You Really Need Chip-Package Co-analysis

There’s only one software company that I know of that covers four major disciplines: Fluids, Structures, Electronics and Systems. That company is ANSYS and when they acquired Apache Design Automation back in 2011 they filled out their products for electronics design, and more specifically in the area of integrated chip-package… Read More

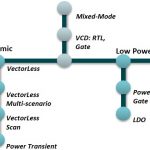

A Complete Simulation Platform for Mobile Systems

If we take an insight into the semiconductor industry, we can easily find that mobile systems are the main drivers of this industry. The Smartphone business has remained at the top since a good number of years. Although the Smartphone sales growth has started showing a sign of stagnation, it is still a main contributor with a solid… Read More

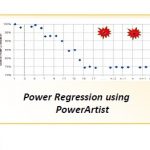

Power Analysis Needs Shift in Methodology

It’s been the case most of the time that until we hit a bottleneck situation, we do not realize that our focus is not at the right spot. Similar is the case with power analysis at the SoC level. Power has become equally if not more important than the functionality and other parameters of an SoC, and therefore has to be verified earlier … Read More