I’ve been noticing over the last few years that electronic design automation (EDA) vendors just love to talk about artificial intelligence (AI) and machine learning (ML), sometimes with deep learning (DL) and neural networks tossed in as well. It can get a bit confusing since these terms are used in two distinct contexts. The first… Read More

Tag: AI

Edge Computing Paradigm

Edge computing is a model in which data, processing and applications are concentrated in devices at the network rather than existing almost entirely in the cloud.

Edge Computing is a paradigm that extends Cloud Computing and services to the of the network, similar to Cloud, Edge provides data, compute, storage, and application… Read More

Big Data Helps Boost PDN Sign Off Coverage

The nearly unavoidable truth about dynamic voltage drop (DVD) signoff for power distribution networks (PDN) is that the quality of results depends on the quality and quantity of the vectors used to activate the circuit switching. As SOCs grow larger and are implemented on smaller nodes, the challenges of sufficient coverage … Read More

Synopsys Expands into Silicon Lifecycle Management

I spoke with Steve Pateras of Synopsys last week to better understand what was happening with their Silicon Lifecycle Management vision, and I was reminded of a Forbes article from last year: Never Heard of Silicon Lifecycle Management? Join the Club. At least two major EDA vendors are now using the relatively new acronym SLM, and… Read More

A Flexible and Efficient Edge-AI Solution Using InferX X1 and InferX SDK

The Linley Group held its Fall Processor Conference 2021 last week. There were several informative talks from various companies updating the audience on the latest research and development work happening in the industry. The presentations were categorized as per their focus, under eight different sessions. The sessions topics… Read More

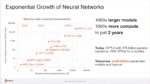

Neural Network Growth Requires Unprecedented Semiconductor Scaling

The truth is that we are just at the beginning of the Artificial Intelligent (AI) revolution. The capabilities of AI are just now starting to show hints of what the future holds. For instance, cars are using large complex neural network models to not only understand their environment, but to also steer and control themselves. For… Read More

Optimize AI Chips with Embedded Analytics

The foundry model, multi-source IP blocks, advanced packaging technologies, cloud computing, hyper-connectivity and access to open-source software have all contributed to the incredible electronics products of recent times. Along with this, the complexity of developing and taking a chip to market has also increased. And… Read More

The Quest for Bugs: “Correct by Design!”

In this article we take an objective view of Virtual Prototyping from the engineering lens and the “quest to find bugs”. In this instance we discuss the avoidance of bugs in terms of architecting complex ASICs to be “correct by design”.

AI Challenges

It is not surprising to find out that other areas of human endeavour, beyond semiconductor… Read More

Enabling Silicon Technologies to Address Automotive Radar Trends and Requirements

During the week of April 19th, Linley held its Spring Processor Conference 2021. The Linley Group has a reputation for putting on excellent conferences. And this year’s spring conference was no exception. There were a number of very informative talks from various companies updating the audience on the latest research and development… Read More

NetApp Simplifies Cloud Bursting EDA workloads

Why burst EDA workloads to the cloud

Time to market challenges are nothing new to those of us who have worked in the semiconductor industry. Each process node brings new opportunities s along with increasingly complex design challenges. 7nm, 5nm and 3nm process nodes have introduced scale, growth, and data challenges at a level… Read More