The Interface IP market has grown with 21% CAGR from 2017 to 2021 and we review the part of this market restricted to the high-end of PCIe, DDR, Ethernet and D2D IP made of PHY and controller targeting the most advanced technology nodes and latest protocol release. We will show that an IP vendor focusing investment on the high-end interconnect… Read More

Tag: 56g serdes

112G/56G SerDes – Select the Right PAM4 SerDes for Your Application

This is another installment covering TSMC’s very popular Open Innovation Platform event (OIP), held on August 25. This event presents a diverse and high-impact series of presentations describing how TSMC’s vast ecosystem collaborates with each other and with TSMC. Not all SerDes are the same. The presentation covered here,… Read More

IBIS-AMI Back-Channel System Optimization in Practice

I recently spent some time at DesignCon 2020 in Santa Clara. For those who haven’t attended this show in a while, you need to go. It’s no longer a small event focused on chip design. It has grown into a true system-level conference, with a broad ecosystem represented on the show floor and in the technical sessions. Ecosystem is an important… Read More

eSilicon Bucking the Trend at OFC with 7nm SerDes

A recent press release from eSilicon caught my eye. The company has been touting their 7nm SerDes quite a bit lately – reach, power, flexibility, things like that. While those capabilities are important, any high-performance chip needs to work in the context of the system, which usually contains technology from multiple sources.… Read More

eSilicon Expands Expertise in 7nm

At SemiWiki we usually don’t write about the press releases we are sent. However, a recent press release by eSilicon caught my eye and prompted me to call Mike Gianfagna, eSilicon Vice President of Marketing. The press release is not just about one thing, rather it focuses on a number of interesting things that together show their… Read More

1.2 Terabit/s C2C Interface? Only with Interlaken!

If you are familiar with high bandwidth networking applications, you probably know this chip-to-chip (C2C) interface protocol. Interlaken architecture, fully flexible, configurable and scalable, is also an elegant answer to the need for very high bandwidth C2C communication. Interlaken is elegant because the protocol … Read More

Samsung Should Just Buy eSilicon Already!

As you all know I’m a big fan of the ASIC business dating back to the start of the fabless semiconductor transformation where anybody could send a design spec to an ASIC company and get a chip back. The ASIC business model also started the smart phone revolution when Samsung built the first Apple SoCs for the iPhones and iPads.

Today … Read More

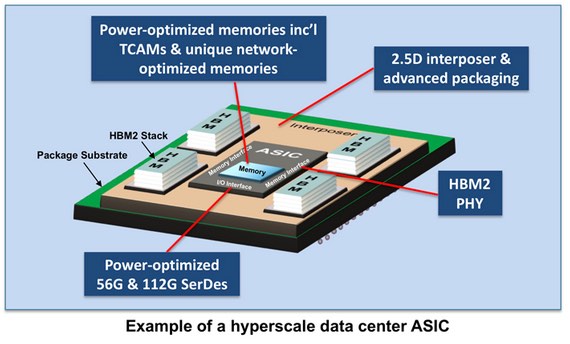

Succeeding with 56G SerDes, HBM2, 2.5D and FinFET

eSilicon presented their advanced ASIC design capabilities at a seminar last Wednesday evening. This event was closed to the press, bloggers and analysts, but I managed to get some details from a friend who attended. The event title was: “Advanced ASICs for the Cloud-Computing Era: Succeeding with 56G SerDes, HBM2, 2.5D and FinFET… Read More