Chip design is getting more difficult as technology advances. Everyone knows that. A lot of the discussion around these issues tends to focus on the demands posed by massive AI workloads and the challenges of shifting to heterogeneous multi-die design. While these create real problems, there is an underlying effect that is making… Read More

Tag: 3nm

Alchip’s Technology and Global Talent Strategy Deliver Record Growth

Alchip Technologies Ltd., a global leader in high-performance computing (HPC) and artificial intelligence (AI) ASIC design and production services, continues its trajectory of rapid growth and technical leadership by pushing the boundaries of advanced-node silicon, expanding its global design capabilities, and building… Read More

IEDM 2025 – TSMC 2nm Process Disclosure – How Does it Measure Up?

Initial thoughts

At IEDM held in December 2024, TSMC presented: “2nm Platform Technology featuring Energy-efficient Nanosheet Transistors and Interconnects co-optimized with 3DIC for AI, HPC and Mobile SoC Applications,” the authors are:

Geoffrey Yeap, S.S. Lin, H.L. Shang, H.C. Lin, Y.C. Peng, M. Wang, PW Wang, CP Lin, KF… Read More

VLSI Technology Symposium – Intel describes i3 process, how does it measure up?

At the VLSI Technology Symposium this week Intel released details on their i3 process. Over the last four nodes Intel has had an interesting process progression. In 2019, 10nm finally entered production with both high performance and high-density standard cells. 10nm went through several iterations eventually resulting in… Read More

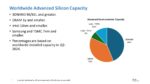

No! TSMC does not Make 90% of Advanced Silicon

Throughout the debate on fab incentives and the Chips Act I keep seeing comments like; TSMC makes >90% of all advanced silicon, or sometimes Taiwan make >90% of all advanced silicon. This kind of ill-defined and grossly inaccurate statement drives me crazy. I just saw someone make that same claim in the SemiWiki forums and… Read More

Pinning Down an EUV Resist’s Resolution vs. Throughput

The majority of EUV production is on 5nm and 3nm node, implemented by late 2022. Metal oxide resists have not been brought into volume production yet [1,2], meaning that only organic chemically amplified resists (CARs) have been used instead until now. These resists have a typical absorption coefficient of 5/um [3,4], which means

ISS 2024 – Logic 2034 – Technology, Economics, and Sustainability

For the 2024 SEMI International Strategy Symposium I was challenged by members of the organizing committee to look at where logic will be in ten years from a technology, economics, and sustainability perspective. The following is a discussion of my presentation.

To understand logic, I believe it is useful to understand what makes… Read More

Analog Bits Enables the Migration to 3nm and Beyond

The world is abuzz with 3nm and 2nm technology availability. These processes offer the opportunity to pack far more on a single die than ever before. The complex digital systems contemplated will bring new AI algorithms to life and much more. But there is another side of the technology migration story. With all that digital processing… Read More

Is Intel cornering the market in ASML High NA tools? Not repeating EUV mistake

- Reports suggest Intel will get 6 of 10 ASML High NA tools in 2024

- Would give Intel a huge head start over TSMC & Samsung

- A big gamble but a potentially huge pay off

- Does this mean $4B in High NA tool sales for ASML in 2024?

News suggests Intel will get 6 of first 10 High NA tools made by ASML in 2024

An industry news source, Trendforce, reports… Read More

Cadence Integrates Power Integrity Analysis and Fix into Design

As integration levels increase, clock frequencies rise, and feature sizes shrink it is not surprising that all or most aspects of semiconductor design become more complex and demand more from design technologies. One example where the traditional approach is breaking down is in optimizing power distribution networks (PDNs)… Read More