Sometimes a standard is a victim of its own success, at least for a while as the economics catch up to the technology. When a standard like USB 3.0 is announced, with a substantial performance increase over USB 2.0, some of the use cases come on board right away. Others, where vendors enjoy a decent ROI with good-enough performance,… Read More

Transaction-based Emulation

Verification has been going through a lot of changes in the last couple of years. Three technologies that used to be largely contained in their own silos have come together: simulation, emulation and virtual-platforms.

Until recently, the workhorse verification tool was simulation. Emulation had its place but limits on capacity… Read More

How to Trim Automotive Sensor?

The electronic content in automotive is exploding, the market for automotive electronics systems is expected to grow from $170 billion in 2011 to $266 billion by 2016 (Strategy Analytics). When you seat in a brand new car, you immediately see the difference with a ten or even five years old vehicle, as you can exercise MP3 music readers,… Read More

End-to-end look at Synopsys ProtoCompiler

Usually, we get the incremental story in news: this new release is x percent better at this or that than the previous release, and so on. Often missing is the big picture, telling how the pieces all tie together. Synopsys took on that challenge in their latest FPGA-based prototyping webinar. … Read More

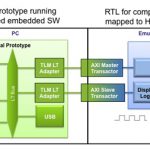

Hybrid Emulation

Hybrid emulation is when part of the system is run in the emulator and part of the system is run in a virtual prototype. Typically a model of the processor(s) is run in the virtual platform and then the rest of the design is modeled by running the RTL on the emulator. I talked to Tom Borgstrom at Synopsys about what technology they have … Read More

Catching IC Manufacturing Defects With Slack-Based Transition Delay Testing

Test engineers are often the unsung heroes in the semiconductor world, because they have the tough job of deciding if each IC is good or bad, while taking the least amount of time on a tester and ensuring that the tests are actually finding and uncovering all manufacturing and process variation defects. Simple stuck-at fault models… Read More

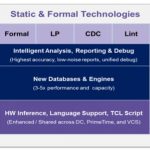

Synopsys Revamps Formal at #51DAC

Synopsys announced verification compiler a couple of months ago and dropped hints about their static and formal verification. They haven’t announced anything much for a couple of years and it turns out that the reason was that they decided that the technology that they had, some internally developed and some acquired, … Read More

Intel Invests in the Fabless Ecosystem!

During my illustrious career one of the most useful axioms that I use just about everyday day is: “Understand what people say but also understand why they are saying it.” This certainly applies to press releases so let’s take a look at what Intel unleashed during #51DAC (in alphabetical order):

ANSYS And Intel Collaborate… Read More

ARC EM DSP supports Always-on Devices

The ARC EM family is the low-power, embedded and low footprint processor part of the larger ARC processor. To target the ultra low-power markets like wearable and IoT, Synopsys has added DSP capabilities to EM5D and EM7D. To be specific, these cores are optimized for ultra low-power control and DSP, thanks to:

- Energy-efficient

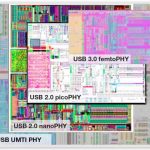

IP Accelerated (Bye Bye EDA 360)

Synopsys has been extremely active, during the last 10 years, not only launching new IP products every year, but also running an ambitious acquisition strategy, with no less than 8 acquisitions. Cascade acquisition bring PCI Express (controller only), when Accelerant bring SerDes (the earth of any PHY IP). The MIPS/Chipidea… Read More