IP-XACT, defined by IEEE 1685, is a standard that pulls together IP packaging, integration, and reuse. For anyone building modern SoCs (Systems on Chip), IP-XACT isn’t just another XML schema: it is a productivity multiplier and a risk-reduction tool that brings order to your electronic system design.

What is IP-XACT?

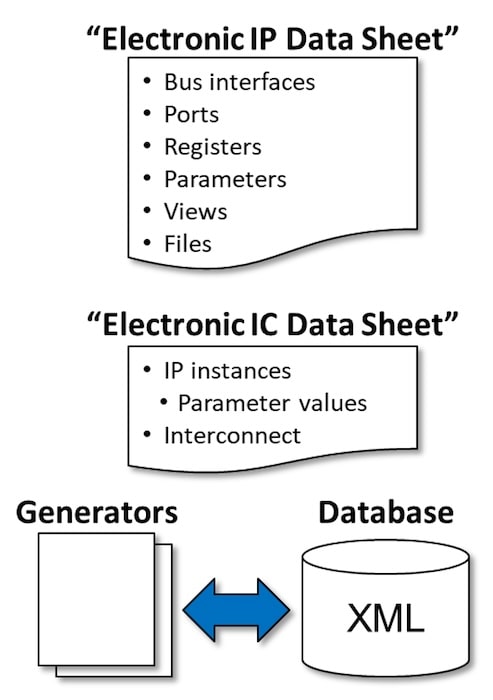

IP-XACT is a flexible, machine-readable format based on XML that captures the structure, interfaces, registers, and configuration of electronic components—IP blocks, subsystems, and full-chip assemblies. By describing everything from register maps and interfaces to bus protocols in a standard language, it eliminates the ambiguity and error-prone processes that have plagued chip integrations for decades.

For IP vendors, IP-XACT offers a consistent delivery forma with metadata, register definitions, and interface specs all described in an interoperable way, minimizing customer confusion and repetitive support. Developers and SoC integrators, benefit from automated integration, reduced manual hand-off mistakes, and easier reuse across multiple projects.

Automation

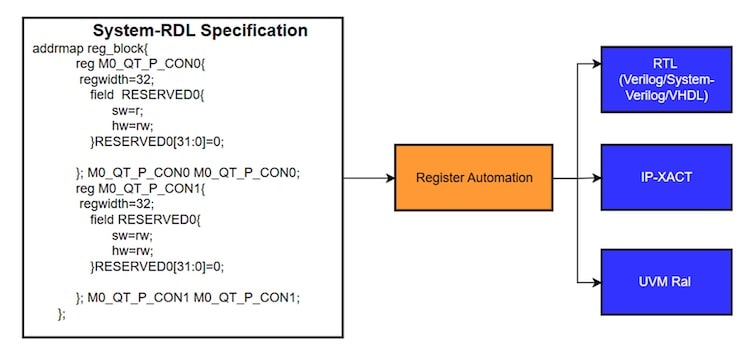

Historically, SoC integration teams used spreadsheets, proprietary formats, or reams of human-written documentation, all of which yield to drift, interpretation, and error. With a growing number of IP blocks—each with its own registers, address maps, and connectivity—managing the complexity by hand is simply unsustainable for modern products. IP-XACT’s standardized representation enables automation: register model generation (both hardware and software), RTL creation, testbench collateral, and design diagrams, all sourced from that single, canonical XML description.

IP-XACT IEEE 1685-2022

The 2022 revision of the standard has plenty of new features to support the ever-increasing complexity of IP-based SoC design:

- Metadata and Memory Modeling: New top-level elements let users define and reuse memory, register, and address blocks, including mode-dependent access rights for registers. Register aliasing and broadcasting are now natively supported, so field sharing across instances is much easier to capture.

- Structured Ports & Mixed-Signal Support: The definition of structured ports means SystemVerilog structs, unions, and interfaces are now first-class citizens. It’s also the first version where analog and mixed-signal ports aren’t vendor hacks but explicitly standardized, crucial for mixed-signal SoCs.

- Power Domains and Low-Power Design: IP-XACT now allows designers to specify power domains and bind instances to those domains, enabling better analysis of power domain crossings—a must for multi-voltage chips.

- API and Automation Enhancements (TGI): The Tight Generator Interface (TGI) now gets RESTful transport, making tool automation and integration more “web ready.” It lets design automators programmatically query, create, and manage IP-XACT elements, from register fields to hierarchical connectivity—crucial for scalable tool flows.

- Simplification: Conditional modeling was deprecated, reducing accidental complexity. Backward compatibility is still possible via extensions, but the intent is a leaner, more predictable modeling experience.

Benefits

The theoretical advantages of IP-XACT translate into measurable outcomes on tape-outs and in the field.

Teams report time-to-market gains—weeks or even months are saved during SoC bring-up and register integration by relying on automated flows as opposed to error-prone scripting or hand-editing. Automated collateral (UVM register models, RTL stubs, C header files, and rich documentation) generated from a single source reduce the risk of inconsistencies between hardware and software—a major cause of late-stage bugs.

Platform SoC teams looking to reuse IPs across derivatives see a scalability improvement. Instead of re-customizing per SoC, IP-XACT lets them start from a known-good baseline and automate the ripple effect of changes across the ecosystem. Collaboration across hardware, firmware, and software teams is no longer stymied by terminology or data format mismatches—everyone works against the same framework.

Scalability

Modern SoC integration relies on stitching together hundreds of IP blocks: processing units, NoCs, memory controllers, PCIe bridges, and peripherals. Each brings its own protocol, data width, and configuration. IP-XACT, paired with automation APIs like TGI, means that this integration becomes not only feasible but repeatable and largely scriptable:

- New IPs (homegrown or licensed) are packaged with canonical XML descriptors.

- Third-party and legacy blocks are adapted by wrapping their specs in IP-XACT.

- System architectures, whether hierarchical or flat, are described in a way that supports tool-driven validation—connectivity checking, register map overlays, power domain consistency, and more.

- Use cases extend from automatic NoC instantiation based on architectural intent, to register automation where SystemRDL or Excel descriptions flow into IP-XACT, then drive the generation of all downstream artifacts.

Best Practices

Success with IP-XACT hinges on a few pragmatic best practices, echoed in real project retrospectives. Insist on third-party IP-XACT collateral that is not only syntactically correct but also semantically meaningful—validate before integration. Extend packaging flows incrementally, starting with simple port descriptions, layering on interfaces, memory maps, multi-view support, and rich file sets. Use TGI and scriptable APIs to automate wherever possible—to reduce manual “glue” logic and focus engineering talent on higher-value problems.

Summary

IP-XACT’s history echoes the industry’s challenge that IP integration is the new bottleneck. The community around the standard, including the Accellera IP-XACT Forum, continues to produce refinements, share best practices, and troubleshoot adoption hurdles. Whether you are a chip architect navigating next-generation SoC complexity or a tool developer enabling the next gain in automation, IP-XACT has proven to be an enabler in the move toward scalable, automated, and reliable semiconductor design.

Related Blogs

- Podcast EP310: On Overview of the Upcoming DVCon Europe Conference and Exhibition with Dr. Mark Burton

- Insider Opinions on AI in EDA. Accellera Panel at DAC

- Accellera at DVCon 2025 Updates and Behavioral Coverage

- Accellera 2024 End of Year Update

Comments

There are no comments yet.

You must register or log in to view/post comments.