As Dan wrote here, we got invited by Intel to IDF and by ARM to a cheeky little party that they organized the day before. I asked ARM if they were announcing anything and they said basically that it would be foolish to make any announcement the week of their biggest competitors big show. Well, that wasn’t a rule that Apple felt like… Read More

Enabling Next-Generation AI Through Advanced Packaging and 3D Fabric IntegrationThe rapid rise of artificial intelligence is fundamentally…Read More

Enabling Next-Generation AI Through Advanced Packaging and 3D Fabric IntegrationThe rapid rise of artificial intelligence is fundamentally…Read MoreChip-Package-System Webinar

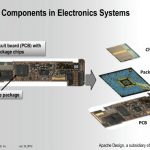

Aveek Sarkar presented a webinar on chip-package-system (CPS) earlier this summer. One of the big challenges with low-power electronic systems is that the performance, power and price goals are mutually conflicting. It’s like the old joke about “pick any 2”. But for a real system all need to be optimized. … Read More

Cadence September News: strong IP and VIP focus

There are three articles on the front page, in the September release of Cadence newsletter, all of them are dedicated to either IP (DDR4), VIP (NVM express VIP being used at Samsung) or Martin Lund. You can read Martin’s interview here and/or take a look at what I write about him this summer. This strong focus on IP, and in fact on Interface… Read More

A Brief History of GLOBALFOUNDRIES

In response to changing industry dynamics, AMD announced in October 2008 a new strategy to focus exclusively on the design phase of semiconductor product development. To achieve that strategy, AMD partnered with Advanced Technology Investment Company (ATIC) of Abu Dhabi to create a new joint venture company designed to become… Read More

Intel Finally Comes Clean on 22nm SoCs!

Ever since Intel announced that they will leverage their advanced process technology leadership into the mobile SoC market I have expressed my doubts. I know how Intel designs their microprocessors, having worked for many of their vendors over the years and having friends at Intel who are actually doing the work. Disclaimer: … Read More

Samsung Invests in Carbon

I’ve talked before about how venture capitalists will no longer invest in EDA companies since the prospect for a huge return just isn’t there any more. By big return I mean an acquisition at hundreds of millions of dollars, like SPC, CCR, Ambit, Cadmos, Simplex. But we all know that chips cannot be designed without software… Read More

Is DDR4 a bridge too far?

We’ve gone through two decades where the PC market made the rules for technology. The industry faces a question now: Can a new technology go mainstream without the PC?

By now, you’ve certainly read the news from Cadence on their DDR4 IP for TSMC 28nm. They are claiming a PHY implementation that exceeds the data rates specified for … Read More

Hogan University: Second Semester

The next event in the Jim Hogan Emerging Companies series (organized by the EDAC Emerging Companies Committee) will be on 17th October at Cadence (I’m guessing in building 5 but I’m sure there will be signs). The specific topic this time will be How to Raise Money and How Not to Spend it. The evening will focus on different… Read More

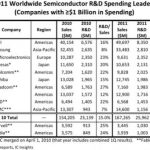

Fabless Semiconductor Ecosystem Update 2012

Just a reminder, the semiconductor industry is doing quite well thanks to the fabless semiconductor ecosystem. TSMC, my economic bellwether, reported another great month with a 32% increase over August 2011 and a 16% increase over January-August 2011. TSMC is forecasting Q3 at a 7% increase over Q2, which was an amazing 21% increase… Read More

Micron ReRAM Patent Alert

Micron recently was awarded patents related to ReRAM. As everyone knows, patents are the lifeblood of technology based industries and the memory business is no different. But what can you learn from a patent? In the first of a series of Blogs, Christie Marrian moderator of the ReRAM-Forum asks that question in the context of patents… Read More

Solving the EDA tool fragmentation crisis