The Linley Group’s Microprocessor conference in Spring is focused on Datacenters now that cloud computing and massive internal datacenters has made them so important. The conference is on February 5th and 6th. It is free to qualified people such as network equipment vendors, network service providers and so on (which … Read More

Chemical Origins of Environmental Modifications to MOR Lithographic ChemistryIn the pursuit of advanced extreme ultraviolet (EUV)…Read More

Chemical Origins of Environmental Modifications to MOR Lithographic ChemistryIn the pursuit of advanced extreme ultraviolet (EUV)…Read More Post-Silicon Validating an MMU. Innovation in VerificationSome post-silicon bugs are unavoidable, but we’re getting…Read More

Post-Silicon Validating an MMU. Innovation in VerificationSome post-silicon bugs are unavoidable, but we’re getting…Read More Securing UALink in AI clusters with UALinkSec-compliant IPA classic networking problem is securing connections with…Read More

Securing UALink in AI clusters with UALinkSec-compliant IPA classic networking problem is securing connections with…Read MoreYou may want to check that known-good RTL

In his blog Coding Horror, Jeff Atwood wrote: “Software developers tend to be software addicts who think their job is to write code. But it’s not. Their job is to solve problems.” Whether the tool is HTML, C, or RTL, the reality is we are now borrowing or buying more software IP than ever, and integrating it into more complex designs,… Read More

Using IC Data Management Tools and Migrating Vendors

Non-volatile memory is used in a wide variety of consumer and industrial applications and comes in an array of architectures like Serial Flash and CBRAM (Conductive Bridging RAM). I caught up with Shane Hollmer by phone this week to gain some insight into a recent acquisition of Atmel’s serial flash components, and how that… Read More

Verdi: No Requiem for Openness

I sat down last week for lunch with Michael Sanie. Mike and I go back a long way, working together at VLSI Technology (where his first job out of school was to take over the circuit extractor that I’d originally written) and then in strategic marketing at Cadence. Now Mike has marketing for (almost?) all of Synopsys’s … Read More

How We Got Here…

Over at the GSA Forum website I have an article on the history of the semiconductor industry. It is actually based on a couple of brief history of semiconductor blogs (here and here) I published here on SemiWiki last year but edited down a lot and tightened up.

Since the start of the year seems to be the time for predictions, here are the… Read More

New PCI Express 3.0 Equalization Requirements

PCI Express 3.0 increased the supported data rate to 8 Gbps, which effectively doubles the data rate supported by PCI Express 2.0. While the data rate was increased, no improvement was made to the channels. As such, an 8 Gbps channel in PCIe 3.0 experiences significantly more loss than one implemented in PCIe 2.0. To compensate for… Read More

First Time, Every Time

While this iconic advertising phrase was first used to describe the ink reliability of a ballpoint pen, it perfectly summarizes the average consumer’s attitude toward automobile reliability as well. We don’t really care how it’s done, as long as everything in our car works first time, every time. Even when that includes heated… Read More

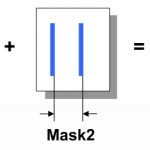

Double Patterning for IC Design, Extraction and Signoff

TSMC and Synopsys hosted a webinar in December on this topic of double patterning and how it impacts the IC extraction flow. The 20nm process node has IC layout geometries so closely spaced that the traditional optical-based lithography cannot be used, instead lower layers like Poly and Metal 1 require a new approach of using two… Read More

FD-SOI is Worth More Than Two Cores

This is the second blog entry about an ST Ericsson white-paper on multiprocessors in mobile. The first part was here.

The first part of the white-paper basically shows that for mobile the optimal number of cores is two. It is much better to use process technology (and good EDA) to run the processor at higher frequency rather than add… Read More

Wall Street Does NOT Know Semiconductors!

In my never ending quest to promote the fabless semiconductor ecosystem I cannot pass up a discouraging word about one of the oldest financial services companies. You can consult with me for $300 per hour to answer your questions about the semiconductor industry on the phone or you can buy me lunch and get it in person (lunch will probably… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era