I recently blogged about the actions filed by Tela Innovations at both the US International Trade Commission (USITC) and in federal district court. Those actions allege that five mobile phone manufacturers -HTC, LG, Motorola Mobility, Pantech, and Nokia – were importing handsets into the US which infringed on seven of… Read More

Siemens Wins Best in Show Award at Chiplet Summit and Targets Broad 3D IC Design EnablementThe recent Chiplet Summit in Santa Clara was…Read More

Siemens Wins Best in Show Award at Chiplet Summit and Targets Broad 3D IC Design EnablementThe recent Chiplet Summit in Santa Clara was…Read More Siemens Fuse EDA AI Agent Releases to Orchestrate Agentic Semiconductor and PCB DesignThough terminology sometimes get fuzzy, consensus holds that…Read More

Siemens Fuse EDA AI Agent Releases to Orchestrate Agentic Semiconductor and PCB DesignThough terminology sometimes get fuzzy, consensus holds that…Read More Verification Analytics: The New Paradigm with Cogita-PRO at DVCON 2026Cogita-PRO, developed by Vtool, introduces a transformative approach…Read More

Verification Analytics: The New Paradigm with Cogita-PRO at DVCON 2026Cogita-PRO, developed by Vtool, introduces a transformative approach…Read More Breker Hosts an Energetic Panel on Spec-Driven VerificationI was fortunate to be asked to moderate…Read More

Breker Hosts an Energetic Panel on Spec-Driven VerificationI was fortunate to be asked to moderate…Read MoreLearning Properties, Assertions and Covers for Hardware Design

How do you learn new hardware design topics? I just got trained online about property-based verification for hardware designers using a free online class at Aldec. The material was created by Jerry Kaczynski, a Research Engineer at Aldec.

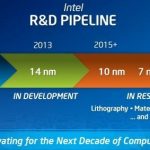

FinFET Design Challenges at 14nm and 10nm

At DAC 2012 we were hearing about the 20nm design ecosystem viability, however IC process technology never stands still so we have early process development going on now at the 10nm and 14nm nodes where FinFET technology is being touted. Earlier in February Vassilios Gerousis, a distinguished engineer at Cadence presented a session… Read More

At DVCon: Pre-Simulation Verification for RTL Sign-Off includes Automating Power Optimization and DFT

By now, you will have seen several postings about all the different activities that are going on at Design and Verification Conference being held Feb. 25-28 at its usual location – the DoubleTree Hotel in San Jose, CA. Besides organizing an experts panel “Where Does Design End and Verification Begin?“, Real… Read More

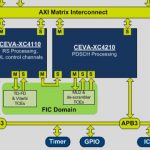

MUST: DSP ready solution for tomorrow smartphone based on CEVA-XC 4000

Like Guiness dark beer, competition is good for you! I mean good for end user, as it pushes DSP IP supplier to provide ever better solution. I am not talking about me-to type of competition, like that we have seen in the past with IBM trying to displace TI at Nokia, by offering a LEAD (DSP IP core from TI used in every NOKIA wireless phone… Read More

How Can You Work Better with Your Foundry?

The fabless revolution in the digital semiconductor industry is no more, with just a few integrated device manufacturers (IDMs) remaining on the playing field, it is now the normal way to do business. However, the learning curve for each new process node continues as it always has, with a host of new technical challenges for the … Read More

Is debugging a task, or a continuous process?

Early in my so-called EE career, I sat in a workshop led by the director of quality for the Ford truck plant in Louisville, KY, where “Quality is Job #1.” At that time, they were gaining experience in electronic control modules (ECMs) for fuel efficiency and emissions control. Who better to transfer the secrets of Crosby and Deming… Read More

Modeling TSV, IBIS-AMI and SERDES with HSPICE

The HSPICE circuit simulator has been around for decades and is widely used by IC designers worldwide, so I watched the HSPICE SIG by video today and summarize what happened. Engineers from Micron, Altera and AMD presented on how they are using HSPICE to model TSVs, IBiS-AMI models and SERDES, respectively.… Read More

Innovative or Die, NoC IP Market is Cruel…

I have blogged in 2011 about the Arteris-Sonics case, initiated by Sonics, claiming that Arteris NoC IP product was infringing Sonics patent. In this article, we have seen that the architecture of Sonics interconnects IP product was not only older but also different from Arteris’ NoC architecture: the products launched initially… Read More

Intel’s x86 – Foundry Breakup Comes into View

The announcement by Intel during their January earnings call that they were going to hike Capex in 2013 over 2012 left many folks scrambling as to the reasons and the what-the hecks? Here was a company that was exiting 2012 with 50% utilization of their advanced 22nm process and yet signaling more building was to come. Furthermore,… Read More

Captain America: Can Elon Musk Save America’s Chip Manufacturing Industry?