Today Micron announced that it is shipping 2GB Hybrid Memory Cube (HMC) samples. The HMC is actually 5 stacked die connected with through-silicon-vias (TSVs). The bottom die is a logic chip and is actually manufactured for Micron in an IBM 32nm process (and doesn’t have any TSVs). The other 4 die are 4Gb DRAM die manufactured… Read More

From the Selfie to Samantha: The Next Trillion-Dollar BehaviorAt CES 2026, Samsung called it a “companion.”…Read More

From the Selfie to Samantha: The Next Trillion-Dollar BehaviorAt CES 2026, Samsung called it a “companion.”…Read More TSMC’s Record Tool Orders Hint at Another CapEx ShockwaveTSMC’s latest Board of Directors capital appropriation announcement…Read More

TSMC’s Record Tool Orders Hint at Another CapEx ShockwaveTSMC’s latest Board of Directors capital appropriation announcement…Read More CEO Interview with Nagesh Gupta of llmda.aiNagesh has built a career spanning multiple aspects…Read More

CEO Interview with Nagesh Gupta of llmda.aiNagesh has built a career spanning multiple aspects…Read More The "New Shift-Left": Why FPGA Prototyping is the Ultimate RISC-V IP SandboxIn the EDA world, "Shift-Left" has traditionally been…Read More

The "New Shift-Left": Why FPGA Prototyping is the Ultimate RISC-V IP SandboxIn the EDA world, "Shift-Left" has traditionally been…Read MoreIntel 14nm versus Samsung 14nm

The legend of Intel being two process nodes ahead of the rest of the industry is quickly coming to an end. To come to terms with this you need to do an apple to apple comparison which is what I will do right here, right now.

First and foremost let’s compare SoC silicon delivery since SoCs are driving the semiconductor industry and will … Read More

Another Major Consolidation in Semiconductor Space!

This time it is between the suppliers of semiconductor manufacturing equipments. And they are among the top ranked global peers. Applied Materials Inc., holding the numero uno position in sales of chip manufacturing equipments in 2012, agreed to acquire Tokyo Electron Ltd, the third in that ranking. Gary Dickerson of Applied… Read More

SystemVerilog Assertions and Functional Coverage

Ashok Mehtahas designed processors at DEC and Intel, managed ASIC vendor relationships, verified networks SoCs, directed engineers at AMCC, and used SystemVerilog since it’s inception. He recently authored a book: SystemVerilog Assertions and Functional Coverage. The book is available in both hardcover and Kindle… Read More

But I Never Have Seen a Synchronizer Failure

You may say, “Why should I worry about synchronizer failures when I have never seen one fail in a product?” Perhaps you feel that the dual-rank synchronizer used by many designers makes your design safe. Furthermore, those chips that have occasional unexpected failures never show any forensic evidence of synchronizer failures.… Read More

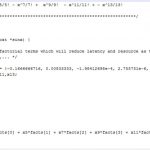

Xilinx’s Vivado HLS Will Float Your FPGA

Very rarely does the FPGA designer, especially with respect to RADAR, think of the FPGA as a floating point processor. Just to be sure I asked my 6 year old and she agreed. But you know what, the Xilinx FPGAs float. Go try it, order some up and fill up the tub.

Anyways I purpose a duel to the avid VHDL coder. I want you to design me a Sine(x) … Read More

A Brief History of Silvaco

Silvaco is the leading supplier of TCAD software, and a major supplier of EDA software for circuit simulation and design of analog, mixed-signal and RF integrated circuits.

The company was founded in 1984 by Dr. Ivan Pesic. The initial product, Utmost, quickly became the industry standard for parameter extraction, device characterization… Read More

Apple: "It’s The Sales Channel, Stupid!"

Apple’s decision to launch the iphone 5C as a “high priced” device as opposed to a $300 entry level mass market consumer play appears to be intertwined in a much more overriding strategic plan that is beginning to play out in the market. Many analysts who pushed for the low cost device saw the need as necessary to save the ecosystem but… Read More

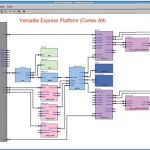

Develop A Complete System Prototype Using Vista VP

Yes, it means complete hardware and software integration, debugging, verification, optimization of performance and power and all other operational aspects of an electronic system in semiconductor design. In modern SoCs, several IPs, RTL blocks, software modules, firmware and so on sit together on a single chip, hence making… Read More

What Does Sports and NoC Have in Common?

As an Oakland Raider season ticket holder I attend as many Raider home games as possible. If you have ever attended a live sporting event at a large stadium, and you travelled by car, you are probably familiar with the traffic problems that occur at the end of the game when everyone wants to leave the stadium parking lot at the same time.… Read More

ASML High-NA EUV is Not Ready for High-Volume Production