It’s common to see an SoC with a few hundred IP blocks today, which is quite a change from full-custom IC designs developed in the early days (i.e. 1980’s) where there was little IP re-use at all. This shift in the technology and business of IP has created a relatively new industry of IP providers from small to large in size.… Read More

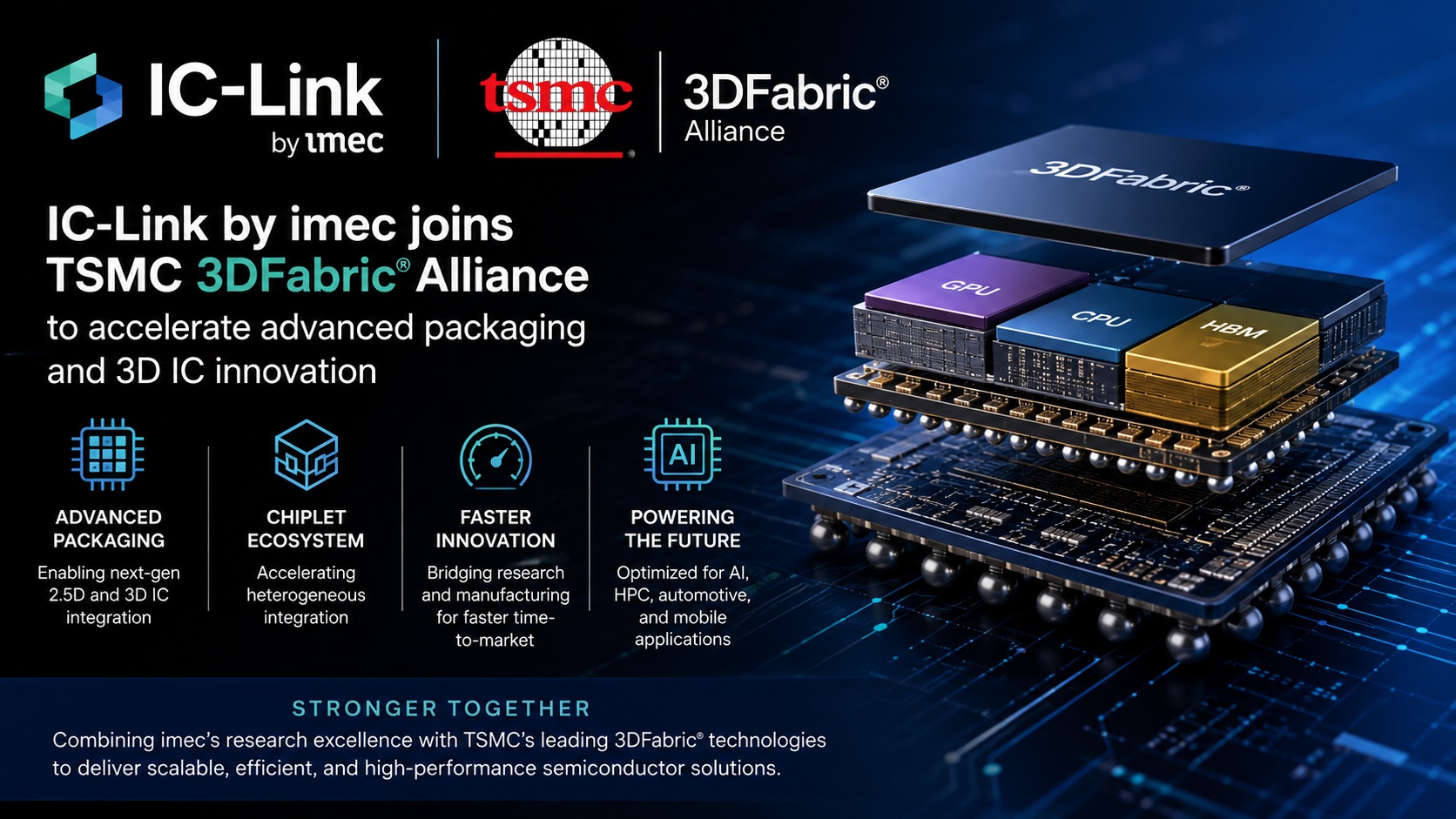

imec IC-Link and TSMC 3DFabric Alliance Expansion Signals New Era of System-Level Scalingimec announced that IC-Link by imec has joined…Read More

imec IC-Link and TSMC 3DFabric Alliance Expansion Signals New Era of System-Level Scalingimec announced that IC-Link by imec has joined…Read More From the Selfie to Samantha: The Next Trillion-Dollar BehaviorAt CES 2026, Samsung called it a “companion.”…Read More

From the Selfie to Samantha: The Next Trillion-Dollar BehaviorAt CES 2026, Samsung called it a “companion.”…Read More TSMC’s Record Tool Orders Hint at Another CapEx ShockwaveTSMC’s latest Board of Directors capital appropriation announcement…Read More

TSMC’s Record Tool Orders Hint at Another CapEx ShockwaveTSMC’s latest Board of Directors capital appropriation announcement…Read More CEO Interview with Nagesh Gupta of llmda.aiNagesh has built a career spanning multiple aspects…Read More

CEO Interview with Nagesh Gupta of llmda.aiNagesh has built a career spanning multiple aspects…Read MoreWhat do Intel and Congress Have in Common?

The war of words continues, when will it end? I consider myself a reasonably educated and informed person, certainly above average by U.S. standards, yet I have no idea why the U.S. Government continues to write checks they cannot cash and I don’t know who to believe in the resulting media blasts. I truly miss the days of Ross… Read More

Catch Mentor’s embedded sessions at ARM TechCon

For Halloween this year, why not tell your embedded software debug horror stories at ARM TechCon? Mentor will have several campfire sessions you should consider attending, but here my Halloween thread breaks down. These three sessions are all quite cheery.

This one, Software Debug on ARM Processors in Emulationis on using emulation… Read More

Spectre from Cadence Goes FastSPICE

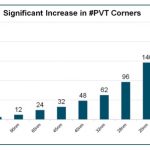

Transistor-level circuit designers have an insatiable appetite to run numerous SPICE circuit simulations in order to determine circuit speed, current and power across Process, Voltage and Temperature (PVT) conditions. Just look at the number of PVT corners increasing as the technology nodes go to 16nm:

The good news today … Read More

Managing Multi-site Design with Cliosoft at LBNL

With the award of the Nobel prize for physics to Higgs (who used to work in the same building at Edinburgh as I did, reflected glory) and Englert yesterday, CERN has been in the news. ClioSoft has an interesting presentation given at CERN about designing a detector chips. The work was done two or three years ago, managed from Lawrence… Read More

Can you Publicly Benchmark EDA Tools?

There is an interesting discussion on SemiWiki in regards to the age old question aboutbenchmarking EDA tools. I remember benchmark discussions at my first DAC in 1984. It was deemed impossible to do a “fair” public benchmark then and it’s not possible now, just my opinion of course but let me tell you why. Simply stated it is a legal,… Read More

Mentor Seminar: Evolution of diagnosis-driven yield analysis

It’s a fact that new process nodes come with some amount of yield challenges. One way to find and eliminate silicon defects is through diagnosis-driven yield analysis (DDYA), which is the topic of a free seminar by Mentor Graphics in Fremont this Thursday, October 10 from 11:30am – 2pm (yes, lunch is included because Mentor… Read More

Atrenta Japan Technoloogy Forum

As they have done for the last few years, Atrenta held its fifth annual user group meeting at the Shin Yokohama Kokusai Hotel on September 13. The attendees are a mixture of customers and other interested members of the semiconductor supply chain. There were nearly 90 people there representing 48 different companies in Japan.

The… Read More

Cadence’s System-to-Silicon Verification Summit

At this year’s DAC, I spoke with several friends at Cadence. I got the distinct impression that something at Cadence had changed. There was a sense of pride and accomplishment that it seems to me had drifted away over the years. Now employees were speaking with true conviction about the accomplishments of the product development… Read More

A Big Thank You to EDA and IP

Electronic Design Automation Software and Semiconductor Intellectual Property are not so much the tail that wags the dog, rather they are like the heart of an elephant, tiny in comparison but without which there is no elephant. There is no doubt that EDA and IP have been key enablers of the semiconductor industry for the past 50 years… Read More

Crossing the Yield Cliff: IDP V6 and the Future of Manufacturing Forecasting