The GSA IP Working Group will meet today in San Jose, and the Group has asked IPnest building a presentation dedicated to Interface IP. The timing was perfect, as I have just completed the “Interface IP Survey” version 5, and I was able to use fresh market data. The IP working group will discover the IP vendor ranking, protocol by protocol,… Read More

From the Selfie to Samantha: The Next Trillion-Dollar BehaviorAt CES 2026, Samsung called it a “companion.”…Read More

From the Selfie to Samantha: The Next Trillion-Dollar BehaviorAt CES 2026, Samsung called it a “companion.”…Read More TSMC’s Record Tool Orders Hint at Another CapEx ShockwaveTSMC’s latest Board of Directors capital appropriation announcement…Read More

TSMC’s Record Tool Orders Hint at Another CapEx ShockwaveTSMC’s latest Board of Directors capital appropriation announcement…Read More CEO Interview with Nagesh Gupta of llmda.aiNagesh has built a career spanning multiple aspects…Read More

CEO Interview with Nagesh Gupta of llmda.aiNagesh has built a career spanning multiple aspects…Read More The "New Shift-Left": Why FPGA Prototyping is the Ultimate RISC-V IP SandboxIn the EDA world, "Shift-Left" has traditionally been…Read More

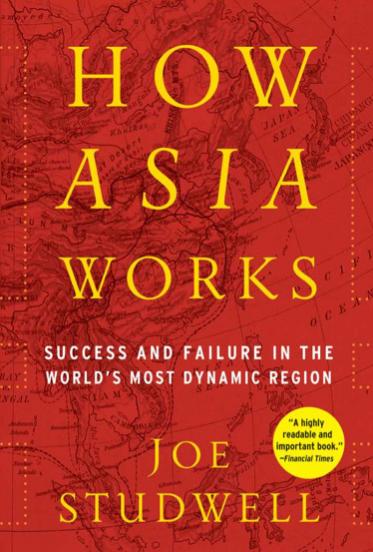

The "New Shift-Left": Why FPGA Prototyping is the Ultimate RISC-V IP SandboxIn the EDA world, "Shift-Left" has traditionally been…Read MoreHow Asia Works, phase 2/3

Success in manufacturing has two conditions: tariff barriers to shield the infant industries from external competition, and a rigorous focus on exports to ensure that manufacturing cannot just shelter behind the tariff barriers and reap monopoly profits inside the country. Each industry needs to have several companies enter,… Read More

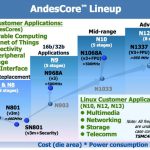

Andes: the Biggest Microprocessor IP Company You’ve Never Hear Of

I wrote in April about Andes Technology, a microprocessor IP licensing company that even the person sitting next to me, a strategic marketing guy from Qualcomm had never heard of. So, OK, if you read that earlier article you had at least heard of them.

Part of the reason you haven’t heard of them is that they are in Taiwan (in Hsinchu)… Read More

Using HLS to Turbocharge Verification

One of the benefits of using high-level synthesis is obviously the ease of writing some algorithms in SystemC since it is at a higher level than RTL (that’s why we call it high-level synthesis!). But a second benefit is at the verification level. Since a lot of the verification gets done at the SystemC level, less needs to be done at … Read More

Always-on Context-aware Sensors in Your Phone

Smartphones are smart but they are about to get smarter. The next big thing in mobile phones is to have a rich sensor environment: proximity, temperature and humidity, atmospheric pressure, light color, cover, gyroscope, magnetometer, accelerometer, ambient light, gesture and more. Some of these are already here, of course,… Read More

How Asia Works, phase 1

This is not too much about semiconductors so consider this an “off-topic” warning. But I think you should read on anyway.

TSMC will show up eventually but not yet.

I was in Asia at last week. Coincidentally, I had a book to read on the plane called How Asia Works by Joe Studwell. It looks at what has made Japan, Korea, Taiwan… Read More

Yes, Intel 14nm Really is Delayed…And They Lost $600M on Mobile

Intel server profits are growing, which isn’t a big suprise. But mobile losses are high. Although the amount lost by the Other Intel Architecture Group had a loss of $606M, that is actually down slightly from Q2 but up a lot from last year when they lost “only” $235M. This group includes Atom, the Infineon Wireless… Read More

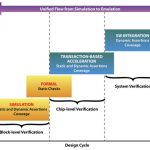

Assertions verifying blocks to systems at Broadcom

Speaking from experience, it is very difficult to get an OEM customer to talk about how they actually use standards and vendor products. A new white paper co-authored by Broadcom lends insight into how a variety of technologies combine in a flow from IP block simulation verification with assertions to complete SoC emulation with… Read More

An ASIC Design Flow at LSI

Harish Aepalais part of the Design Closure Methodology group at LSIand he recently talked about his ASIC handoff experience in a webinar. Harish works with logic and physical synthesis, timing constraints, RTL analysis and formal verification.

One challenge with ASIC handoff has been getting through design closure with the… Read More

SEMI Smart Technology Conference

I should start by saying that SEMI Smart Technology is not technology that is only half as smart as our phones, it is a conference on smart technology organized by SEMI. Officially it is called the International Technology Partners Conference with a sort of subtitle of From Smart Cars to Smart Cities: Shaping the Future of Microelectronics… Read More

ASML High-NA EUV is Not Ready for High-Volume Production