QCOM is now sampling the TSMC 20nm version of its market dominating Gobi LTE modem. The announcement also included a new turbo charged version of their 28nm Snapdragon 800 SoC with a Krait 450 quad core CPU and Adrino 420 GPU. Given the comparable benchmarks between the Intel 22nm SoC and the 28nm SoCs from Apple and QCOM, the new 20nm… Read More

From the Selfie to Samantha: The Next Trillion-Dollar BehaviorAt CES 2026, Samsung called it a “companion.”…Read More

From the Selfie to Samantha: The Next Trillion-Dollar BehaviorAt CES 2026, Samsung called it a “companion.”…Read More TSMC’s Record Tool Orders Hint at Another CapEx ShockwaveTSMC’s latest Board of Directors capital appropriation announcement…Read More

TSMC’s Record Tool Orders Hint at Another CapEx ShockwaveTSMC’s latest Board of Directors capital appropriation announcement…Read More CEO Interview with Nagesh Gupta of llmda.aiNagesh has built a career spanning multiple aspects…Read More

CEO Interview with Nagesh Gupta of llmda.aiNagesh has built a career spanning multiple aspects…Read More The "New Shift-Left": Why FPGA Prototyping is the Ultimate RISC-V IP SandboxIn the EDA world, "Shift-Left" has traditionally been…Read More

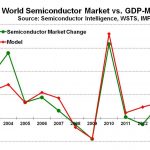

The "New Shift-Left": Why FPGA Prototyping is the Ultimate RISC-V IP SandboxIn the EDA world, "Shift-Left" has traditionally been…Read MoreSemiconductor market could grow 15% in 2014

The global semiconductor market has grown 4% for the first three quarters of 2013 compared to a year ago, according to World Semiconductor Trades Statistics (WSTS). Guidance for 4Q 2013 revenue change versus 3Q 2013 varies widely for key semiconductor companies. Texas Instruments (TI), Broadcom, Infineon and Renesas all expect… Read More

The Rosetta Stone of Lithography

At major EDA events, CEDA (the IEEE council on EDA, I guess you already know what that bit stands for) hosts a lunch and presentation for attendees and others. This week was ICCAD and the speaker was Lars Liebmann of IBM on The Escalating Design Impact of Resolution-Challenged Lithography. Lars decided to give us a whirlwind tour … Read More

Revisiting Andy Grove’s "Only the Paranoid Survive"

Over the course of the last fifty years there have been two significant books that have delivered emotional and operational clarity on the rise and fall of high tech companies and industries: The Innovator’s Dilemma and Only the Paranoid Survive. Amazingly, these two books were released within a year of each other (1996, 1997) … Read More

IoT begets silicon, interoperability, and standards

The Internet of Things is on every technology mind these days, but what does it mean for the EDA community? Dennis Brophy of Mentor Graphics says the billions of things we are hearing about will not happen unless we find a way to build a lot more things, efficient things, and connected things. He has more thoughts in our recent interview.… Read More

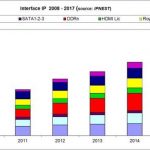

Interface Protocols, USB3, PCI Express, MIPI, DDRn… the winner and losers in 2013

How to best forecast a specific protocol adoption? One option is to look at the various IP sales, it will give you a good idea of the number of SoC or IC offering this feature on the market in the next 12 months. Once again, if you wait for the IP sale to have reached a maximum, it will be too late, so you have to monitor the IP sales dynamic when… Read More

Meeting the Challenges of Designing Internet of Things SoCs with the Right Design Flow and IP

Connecting “things” to the Internet and enabling sensing and remote control, data gathering, transmission, and analysis improves many areas: safety and quality of life, healthcare, manufacturing and service delivery, energy efficiency, and the environment. The concept of the Internet of Things (IoT) is quickly becoming… Read More

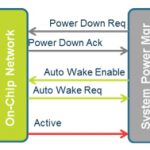

5 Rules of Power Management Using NoCs

If it has escaped your notice that power management on SoCs is important then you need to get out more. Increasingly, the complexity of the interconnect between the various processors, memories, offload processors, devices, interfaces and other blocks means that the best way to implement it is to use a network on chip (NoC). But… Read More

Design Methodology and its Impact on the Future of Electronics

Today at the Semisrael Expo 2013 (in Israel of course) Ajoy Bose gave a keynote on how design methodology will impact electronics. The big pictures is that microelectronics is driven by some major disruptive forces and, as a result, technology and industry are evolving dramatically, which creates a need for research and innovation… Read More

Raptor Image Signal Processor

This fall there seems to be a bumper harvest of cores. Today Imagination Technologies announced their latest core for image signal processing. Like all of their cores, it is designed to be part of an SoC and is designed to work with other Imagination cores to build a complete image processing system. In particular, it is designed … Read More

ASML High-NA EUV is Not Ready for High-Volume Production