You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

Social Media at Silvacoby Daniel Payne on 12-21-2013 at 4:58 pmCategories: EDA

Founded back in 1984, Silvaco has been in business for some 29 years now, focusing on the TCAD and EDA markets.

Browsing their Home page at www.silvaco.com we find four social media links in the footer: Facebook, Twitter, YouTube and LinkedIn.… Read More

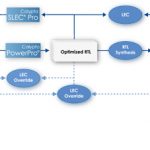

SLEC is Not LECby Paul McLellan on 12-20-2013 at 3:00 pmCategories: EDA

One of the questions that Calypto is asked all the time is what is the difference between sequential logical equivalence checking (SLEC) and logical equivalence checking (LEC).

LEC is the type of equivalence checking that has been around for 20 years, although like all EDA technologies gradually getting more powerful. LEC is … Read More

As I see the semiconductor industry going through significant changes and advances, yet ironically plagued by a growing perception that the pace of scaling is slowing, I was inclined to take a peek into what the industry experts say about the state of the industry and the future of Moore’s Law. Fortunately, at last week’s International… Read More

2013 was an up year for the stock markets as both the DJIA and the tech-heavy NASDAQ showed significant growth, so how did EDA and Semi IP companies do in the past 12 months? A quick stock plot from Yahoo Finance shows us that only two of the seven companies beat the NASDAQ: ARMH, MENT.… Read More

Global semiconductor manufacturing equipment sales have increased each of the last three quarters after dropping significantly in the second half of 2012, based on data from Semiconductor Equipment and Materials International (SEMI) and Semiconductor Equipment Association of Japan (SEAJ). Much of the volatility is in sales… Read More

The hottest real estate? Your wrist!by Beth Martin on 12-19-2013 at 3:28 pmCategories: General

I first read about the Pebble smartwatch earlier this year and thought “I don’t need yet another electronic device, and certainly not one that’s attached to my body.” Then I felt bad. Am I a troglodyte? It’s true, I do still have an iPhone 4, which is a little embarrassing in Silicon Valley. I have also never worn a wrist watch of any kind,… Read More

I spend about an hour a day reading blogs from EDA companies, foundries, independent bloggers and of course, SemiWiki. Richard Goering at Cadence assembled a top 10 list of the most popular blogs posted on their site in 2013, revealing that engineers were most interested in: FinFETs, 20nm and smaller nodes, memory technology and… Read More

The first keynote at the Burlingame 3D conference was by Doug Yu of TSMC. Not surprisingly he was talking about 3D. In particular, TSMC has WLSI technology that they call CoWoS, which stands for chip-on-wafer-on-substrate which pretty much describes how it is built. This is the technology that Xilinx uses for its recently announced… Read More

We have posted several blogs related to Cadence IP strategy, or I should say new strategy. Each of these blogs was dealing with a particular product, like PCI Express gen-3 Controller IP, latest DDR4 Memory Controller or Wide I/O. This approach was equivalent to describe trees, one after one, and finally ignoring the forest! It’s… Read More

It was a dinner with more than a thousand semiconductor professionals from around the world keynoted by Author and Editor in Chief of Forbes Magazine Steve Forbes. What more could a humble blogger ask for? Even at $250 a plate it was well worth it just to mingle amongst the people who make this industry so great.

Global Semiconductor… Read More

ASML High-NA EUV is Not Ready for High-Volume Production