Samsung’s aggressive marketing is starting to hit the fabless semiconductor ecosystem so we had all better be prepared. Samsung’s 2012 marketing budget exceeded $400M which probably beats the marketing budget of the entire fabless ecosystem! The question is, will the fabless semiconductor industry be easily swayed by Samsung’s… Read More

Reachability in Analog and AMS. Innovation in VerificationCan a combination of learning-based surrogate models plus…Read More

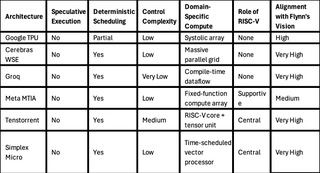

Reachability in Analog and AMS. Innovation in VerificationCan a combination of learning-based surrogate models plus…Read More Flynn Was Right: How a 2003 Warning Foretold Today’s Architectural PivotIn 2003, legendary computer architect Michael J. Flynn…Read More

Flynn Was Right: How a 2003 Warning Foretold Today’s Architectural PivotIn 2003, legendary computer architect Michael J. Flynn…Read More Enabling RISC-V & AI Innovations with Andes AX45MPV Running Live on S2C Prodigy S8-100 Prototyping SystemQualifying an AI-class RISC-V SoC demands proving that…Read More

Enabling RISC-V & AI Innovations with Andes AX45MPV Running Live on S2C Prodigy S8-100 Prototyping SystemQualifying an AI-class RISC-V SoC demands proving that…Read More DAC News – A New Era of Electronic Design Begins with Siemens EDA AIAI is the centerpiece of DAC this year.…Read More

DAC News – A New Era of Electronic Design Begins with Siemens EDA AIAI is the centerpiece of DAC this year.…Read MoreUnlocking the Full Potential of Soft IP

EDA vendors, IP suppliers and Foundries provide an eco-system for SoC designers to use in getting their new electronic products to market quicker and at a lower cost. An example of this eco-system are three companies (TSMC, Atrenta, Sonics) that teamed up to produce a webinar earlier in March called: Unlocking the Full Potential… Read More

A Brief History of Forte Design Systems

When Semiwiki readers see the name Forte Design Systems, they may think of the live bagpipers’ performance that closes the yearly Design Automation Conference. Forte has been the sponsor of this moving end to DAC since 2001. Step with me behind the plaid kilts for a good look at this remarkable company headquartered in San Jose, … Read More

Mixed-Signal SoC verification has integrated solution

These days when we talk of SoC verification, what comes to our mind immediately is VirtualPlatform. Of course with the increasing size, complexity and different styles of designs, it is very much a need.

However, that is supported by actual verification engines and methodologies which are varying considerable with digital, … Read More

Data Management for Designers

Back when I was a programmer at VLSI Technology in the mid-1980s, I was responsible for all the data management in the VLSI Design Tools. By responsible for, I mean that I designed the whole system and wrote all the code. Prior to the 5th release of our product, there was no data management, designers simply used filenames and it was … Read More

Simon Segars to be New CEO of ARM

ARM announced today that Warren East, the CEO, would be retiring at the end of June. The new CEO will be Simon Segars, currently President of ARM and the de facto #2 guy. Currently Simon is based in the US and I don’t know if he plans to return to Britain or not. But he will live what will inevitably be a lifestyle that involves crossing… Read More

View from the top: Brad Quinton

Many engineers dream about starting their own company some day, and today I talked with an engineer that has gone beyond the dreaming stage to actually start an EDA company and then get that company acquired. His name is Brad Quinton and the start-up was called Veridae Systems, now part of Tektronix.

Brad Quinton… Read More

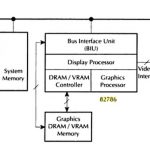

Interconnect Optimization of an SoC Architecture

My last chip design at Intel was a GPU called the 82786and the architects of the chip wrote a virtual prototype using the MAINSAIL language. By using a virtual prototype they were able to:

- Simulate bus traffic, video display and video RAM

- Determine throughput

- Measure latency

- Verify that bus priorities were working

- Optimize the

Wally Rhines, Victor Peng and Chenming Hu to Speak at Mentor User2User Conference

This year’s Mentor Graphics user group meeting, User2User, will be held at the DoubleTree by Hilton in San Jose, California on April 25, 2013. The featured keynote presenters include…

- Dr. Walden C. Rhines, CEO and Chairman of Mentor Graphics, talking about “Organizing by Design”

- Victor Peng, Senior VP, Xilinx presenting on “The

Speech Recognition : Can it be the next game changer?

The cell phone phenomena has catalyzed the technology growth and coaxed the hardware and software to work more closely. The Apple effect further directed this technology growth to focus on enhanced user experience. The emphasis has been primarily on the display and touch aspects of the designs with limited adoption on other areas.… Read More

Flynn Was Right: How a 2003 Warning Foretold Today’s Architectural Pivot