…then you should read about this benchmark result showing how digital power varies with process corners, for high-speed data networking chip, not exactly the type of IC targeting mid-performance mobile application. Before discussing the benchmark results, we need to have some background about this kind of ASIC chip. Such a … Read More

CEO Interview with Nagesh Gupta of llmda.aiNagesh has built a career spanning multiple aspects…Read More

CEO Interview with Nagesh Gupta of llmda.aiNagesh has built a career spanning multiple aspects…Read More The "New Shift-Left": Why FPGA Prototyping is the Ultimate RISC-V IP SandboxIn the EDA world, "Shift-Left" has traditionally been…Read More

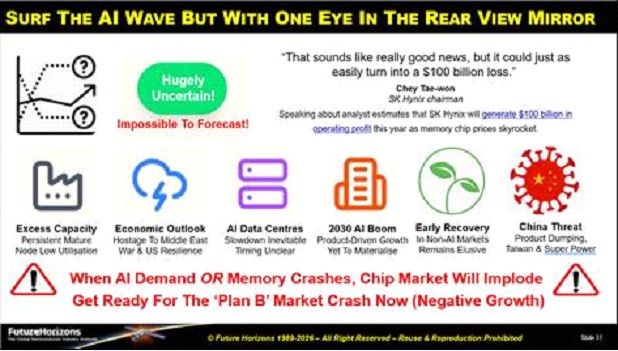

The "New Shift-Left": Why FPGA Prototyping is the Ultimate RISC-V IP SandboxIn the EDA world, "Shift-Left" has traditionally been…Read More The Semiconductor Growth Numbers are Insane but the Real World Doesn’t Tally!May’s WSTS Report saw March’s total monthly semiconductor…Read More

The Semiconductor Growth Numbers are Insane but the Real World Doesn’t Tally!May’s WSTS Report saw March’s total monthly semiconductor…Read More SiFive’s P570 Gen 3 Pushes RISC-V Further Into the AI EraWith the launch of its new P570 Gen…Read More

SiFive’s P570 Gen 3 Pushes RISC-V Further Into the AI EraWith the launch of its new P570 Gen…Read More CEO Interview with Dr. Jekaterina Viktorova of SyentaDr. Jekaterina (Jeka) Viktorova is the CEO and…Read More

CEO Interview with Dr. Jekaterina Viktorova of SyentaDr. Jekaterina (Jeka) Viktorova is the CEO and…Read MoreData Outgrowing Datacenter Performance

Last week I attended the Linley Datacenter Conference. This is not the conference on mobile which is not until April. However, a lot of the growth in datacenter is driven by mobile, with the increasing dominance of the model where data is accessed by smartphones but a lot of the backend computing and datastorage is in the cloud.

From… Read More

Update on AMS Verification at DVcon

Digital verification of SoCs is a well-understood topic and there’s a complete methodology to support it, along with many EDA vendor tools. On the AMS (Analog Mixed-Signal) side of the design world life is not so easy, mostly because there are no clear standards to follow.

To gain some clarity into AMS verification I spoke… Read More

TI – The Initial Innovator of Semiconductor ICs

[TI’s China Foundry acquired from SMIC]

During my engineering graduation, electronic design courses and mini-projects, the ICs I used to come across were SN 7400 series from Texas Instrumentsthat covered a large range of devices from basic gates and flip-flops to counters, registers, memories, ALUs, system controllers, and… Read More

Has LinkedIn Jumped the Shark?

LinkedIn is without a doubt the number one social network for semiconductor professionals. Based on my experience, the big LinkedIn boom came with the massive unemployment during the Great Recession of 2009. In my estimate, unemployment was 12%+ at the high point in Silicon Valley and resumes clogged the internet with LinkedIn… Read More

Who Won the DesignVision Awards at DesignCon this year?

The Seattle Seahawks had an awesome victory in the SuperBowl against the Denver Broncos, so folks living here in the Pacific Northwest are feeling proud and optimistic. The recent DesignConconference and exhibit ended 10 days ago and there were also victors announced in terms of the annual DesignVision awards that have three … Read More

What does a 52% increase in DSP IP core licensing means?

The future market performance for an IP vendor licensing an IP based on a model with upfront fee plus royalties can be easily and safely evaluated if you look at the first part of revenue: upfront fee. Even if the royalty part is declining, exhibiting a 52% increase (Q4 2013 to Q4 2012) in upfront licensing fee is a promise that the future… Read More

Verification Execution: When will we get it right?

Verification technologist Hemendra Talesaraattended a conference in Austin and asked me to post this article on verification execution for him as a blog. I first met Hemendra when he worked at XtremeEDA, and now he works at Synapse Design Automation – a design services company.

“In theory there is no difference between … Read More

Verification Execution: When will we get it right?

Verification technologist Hemendra Talesaraattended a conference in Austin and asked me to post this article on verification execution for him as a blog. I first met Hemendra when he worked at XtremeEDA, and now he works at Synapse Design Automation – a design services company.

“In theory there is no difference between … Read More

SoC Verification Closure Pushes New Paradigms

In the current decade of SoCs, semiconductor design size and complexity has grown by unprecedented scale in terms of gate density, number of IPs, memory blocks, analog and digital content and so on; and yet expected to increase further by many folds. Given that level of design, it’s imperative that SoC verification challenge has… Read More

From the Selfie to Samantha: The Next Trillion-Dollar Behavior