On SemiWiki we have some 247 blogs and forum discussions on the topic of “automotive“, so I’m pleased to learn that at DAC in San Francisco there is a new track just for automotive systems and software. Just consider all of that electronic content in your typical auto:… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data CenterAt the TERAFAB launch event in Austin on…Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data CenterAt the TERAFAB launch event in Austin on…Read More Synopsys Advances Hardware Assisted Verification for the AI EraAt the 2026 Synopsys Converge Event, Synopsys announced…Read More

Synopsys Advances Hardware Assisted Verification for the AI EraAt the 2026 Synopsys Converge Event, Synopsys announced…Read More Chemical Origins of Environmental Modifications to MOR Lithographic ChemistryIn the pursuit of advanced extreme ultraviolet (EUV)…Read More

Chemical Origins of Environmental Modifications to MOR Lithographic ChemistryIn the pursuit of advanced extreme ultraviolet (EUV)…Read More Post-Silicon Validating an MMU. Innovation in VerificationSome post-silicon bugs are unavoidable, but we’re getting…Read More

Post-Silicon Validating an MMU. Innovation in VerificationSome post-silicon bugs are unavoidable, but we’re getting…Read MoreWill IoT Drive the Next Semiconductor Revolution?

To further my quest to comprehend the latest trends in the semiconductor industry continues, I spent the morning with SEMI at the “The Silicon Valley Breakfast Forum: Internet of Things (IoT) – Driving the Microelectronics Revolution” seminar. I’m a big fan of the breakfast seminar concept. I’m up early anyway and it is … Read More

Show Me How To Get Better DRC and LVS Results For My SoC Design

Most IC engineers learn best by hands-on experience when another more experienced person can show us what to do. If you cannot find that experienced person, then the next best thing is a video from an expert. I was surprised to find out that video was so important today that the #2 most viewed web site on the Internet was www.youtube.com… Read More

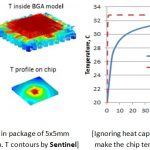

Fast & Accurate Thermal Analysis of 3D-ICs

As Moore’s law started saturating on a single semiconductor die, the semiconductor community came up with the approach of growing vertically by stacking dies one above other in a 3D-IC arrangement. However, a major concern with a 3D-IC is that the heat generated by each die can get trapped in the stack, and hence it’s extremely important… Read More

A Brief History of Functional Verification

Usually these brief history pieces are totally written by the SemiWiki blogger whose name is at the top. Often me since that was how I prototyped book chapters (buy). Well, OK, I did actually write this but it is completely cribbed from a presentation earlier this week by Wally Rhines who gave a sort of keynote at the announcement of… Read More

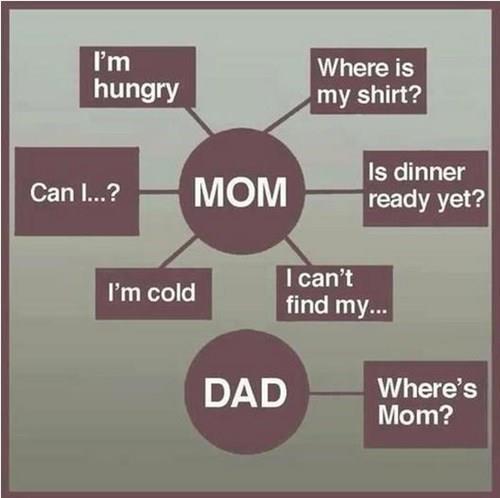

Semiconductor Meme Contest!

Hopefully we all know what memes are, if not, ask one of your children or grandchildren. Having four grown children of my own I see memes posted on my FaceBook page now and again in support of my superior parenting skills. Remember when EETimes used to run a picture and readers would send in funny captions? An early form of meme, not that… Read More

Expert Constraint Management Leads to Productivity & Faster Convergence

The SoC designs of today are much more complex than ever in terms of number of clocks, IPs, levels of hierarchies, several modes of operations, different types of validations and checks for growing number of constraints at various stages in the design flow. As a semiconductor design evolves through several stages from RTL to layout,… Read More

4G shalt thou not count, neither count thou 2G

Five years from now, what will be the leading mobile connectivity standard? If you said 4G, please report to the brainwashing remediation center nearest you immediately. 3G is not only here to stay for the long haul, it’s growing – and will quickly become the preferred choice for M2M deployments.… Read More

U2U: Things You Might Not Know About TSMC

At Mentor’s U2U this afternoon I attended a presentation on TSMC’s use of Calibre PERC (it is a programmable electrical rule checker) for qualification of IP in TSMC’s IP9000 program. I’ve written about this before here. Basically IP providers at N20SOC, N16FF, and below are required to use PERC to guarantee… Read More

GSA 3DIC

At the GSA Silicon Summit this afternoon there was a discussion of 3D IC and 2.5D IC. The session was moderated by Javier DeLaCruz of eSilicon and the panelists were:

- Calvin Cheung of ASE (an OSAT)

- Gil Lvey of OptimalTest (a test house)

- Bob Patti of Tezzaron (semiconductor company specializing in TSV-based designs)

- Riko Radojcic

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center