Please join me for an IP conversation in collaboration with ClioSoft on Wednesday, April 30th, 2014 @ 11:00 AM PST. At the EDPS Workshop IP day there were two interesting presentations on IP reuse. The first one was by Warren Savage of IPextreme: Top Ten Reasons Why Internal IP Reuse Fails. The second was by Ranjit Adhikary of ClioSoft:… Read More

Siemens Wins Best in Show Award at Chiplet Summit and Targets Broad 3D IC Design EnablementThe recent Chiplet Summit in Santa Clara was…Read More

Siemens Wins Best in Show Award at Chiplet Summit and Targets Broad 3D IC Design EnablementThe recent Chiplet Summit in Santa Clara was…Read More Siemens Fuse EDA AI Agent Releases to Orchestrate Agentic Semiconductor and PCB DesignThough terminology sometimes get fuzzy, consensus holds that…Read More

Siemens Fuse EDA AI Agent Releases to Orchestrate Agentic Semiconductor and PCB DesignThough terminology sometimes get fuzzy, consensus holds that…Read More Verification Analytics: The New Paradigm with Cogita-PRO at DVCON 2026Cogita-PRO, developed by Vtool, introduces a transformative approach…Read More

Verification Analytics: The New Paradigm with Cogita-PRO at DVCON 2026Cogita-PRO, developed by Vtool, introduces a transformative approach…Read More Breker Hosts an Energetic Panel on Spec-Driven VerificationI was fortunate to be asked to moderate…Read More

Breker Hosts an Energetic Panel on Spec-Driven VerificationI was fortunate to be asked to moderate…Read MoreDigital, Analog, Software, IP – Isn’t it all just the same?

Designing an SoC requires a team, and the engineers typically use lots of specialized EDA software and semiconductor IP to get the job done. Many have started to ask about how designing a chip is different than designing and managing a large software project, or how is analog design different than digital design in terms of managing… Read More

Dr. Morris Chang: A Conversation with the Chairman

There are moments in one’s career that are memorable beyond others, and last night was one of those moments for me, absolutely:

Stanford University President John L. Hennessy will lead a discussion with Stanford Engineering Hero Morris Chang, an innovator and entrepreneur who revolutionized the semiconductor industry by creating… Read More

Strong 2014 for Semiconductor Equipment and CapEx

Spending on semiconductor manufacturing equipment is headed for healthy growth in 2014. The latest data from SEMI and the Semiconductor Equipment Association of Japan (SEAJ) shows March 2014 three-month-average billings for semiconductor manufacturing equipment were up 16% from February 2014 and up 31% from a year ago. Bookings… Read More

Shorten Time to Market for NVM Express Based Storage Solution

A number of technical and business trends are converging to create a booming market for solid state drives (SSDs), with gigabytes of flash memory capacity along with the related control electronics packaged in the form factor of a 1.8”‐, 2.5”‐ or 3.5”. storage device. The first is the emergence of tablets and pervasiveness of smart… Read More

ARM Results, Strong Biceps

ARM announced their Q1 results yesterday. Having just written that Intel lost $1B in mobile, I guess I could have used the title “ARM didn’t lose $1B in mobile.” They made $100M (on revenues of $300M). So let’s start off with what their results actually were and then look at what other things of interest … Read More

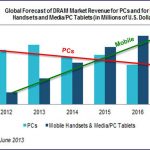

Welcome, LPDDR4!

Thanks to memory controller expert Marc Greenberg, Marketing Director for DDRn Controller IP with Synopsys, for this post “Qualcomm announces first application processor with LPDDR4 capability”. According with Marc, this Application Processor, the Snapdragon 810, is “the first product that I’m aware of that will use LPDDR4… Read More

Learning an HDL Simulator

Learning an HDL language or an HDL simulator are two different things, so I wanted to see what was available for learning a vendor-specific HDL simulator. I’ve already taught Verilog as an instructor using both ModelSim and Active-HDL simulators, however we only used a handful of commands in the class and labs in order to … Read More

IP the eSilicon Way

Pop quiz: eSilicon has a big IP development group in what Asian country? If you didn’t know and you guessed, you probably got it wrong with China or India. It is Vietnam. In fact they have two sites. One in Ho Chi Minh City (that used to be called Saigon) and one in Da Nang.

At Electronic Design Process Symposium (EDPS) held last … Read More

You didn’t say it has to work

“Failure to plan is planning to fail.” If that is true – and it has been quoted verbatim or slightly modified so many times throughout modern history, there has to be some truth – why does most of the engineering community seem to detest planning so much?

Engineering planning doesn’t mean whipping out a block diagram or pseudo code,… Read More

Captain America: Can Elon Musk Save America’s Chip Manufacturing Industry?