Engineered substrate technology is driving an evolution within the semiconductor industry. As Moore’s Law reaches its limits, the focus is shifting from traditional planar wafer scaling to innovative material engineering and 3D integration. Companies like Soitec, Intel and Samsung are pioneering this transition, unlocking… Read More

Scaling Multi-Die Connectivity: Automated Routing for High-Speed InterfacesThis article concludes the three-part series examining key…Read More

Scaling Multi-Die Connectivity: Automated Routing for High-Speed InterfacesThis article concludes the three-part series examining key…Read More Arteris Highlights a Path to Scalable Multi-Die Systems at the Chiplet SummitAt the recent Chiplet Summit, presentations, discussions and…Read More

Arteris Highlights a Path to Scalable Multi-Die Systems at the Chiplet SummitAt the recent Chiplet Summit, presentations, discussions and…Read More Captain America: Can Elon Musk Save America's Chip Manufacturing Industry?Intel has posted three consecutive years of falling…Read More

Captain America: Can Elon Musk Save America's Chip Manufacturing Industry?Intel has posted three consecutive years of falling…Read MorePodcast EP276: How Alphawave Semi is Fueling the Next Generation of AI Systems with Letizia Giuliano

Dan is joined by Letizia Giuliano, Vice President of Product Marketing and Management at Alphawave Semi. She specializes in architecting cutting-edge solutions for high-speed connectivity and chiplet design architecture. Prior to her role at Alphawave Semi, Letizia held the position of Product Line Manager at Intel, where… Read More

CEO Interview: Dr. Andreas Kuehlmann of Cycuity

Dr. Andreas Kuehlmann, Executive Chairman and CEO at Cycuity, has spent his career across the fields of semiconductor design, software development, and cybersecurity. Prior to joining Cycuity, he helped build a market-leading software security business as head of engineering at Coverity and, after its acquisition by Synopsys,… Read More

The Double-Edged Sword of AI Processors: Batch Sizes, Token Rates, and the Hardware Hurdles in Large Language Model Processing

Unlike traditional software programming, AI software modeling represents a transformative paradigm shift, reshaping methodologies, redefining execution processes, and driving significant advancements in AI processors requirements.

Software Programming versus AI Modeling: A Fundamental Paradigm Shift

Traditional… Read More

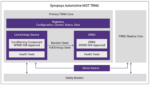

TRNG for Automotive achieves ISO 26262 and ISO/SAE 21434 compliance

The security of a device or system depends mainly on being unable to infer or guess an alphanumeric code needed to gain access to it or its data, be that a password or an encryption key. In automotive applications, the security requirement goes one step further – an attacker may not gain access per se, but if they can compromise vehicle… Read More

Is Arteris Poised to Enable Next Generation System Design?

The semiconductor ecosystem is changing. Monolithic design is becoming multi-die design. Processors no longer inform software development options. It’s now the other way around with complex AI software informing the design of purpose-built hardware. And all that special-purpose hardware needs drivers to make it come to … Read More

Bug Hunting in Multi Core Processors. Innovation in Verification

What’s new in debugging multi-/many-core systems? Paul Cunningham (GM, Verification at Cadence), Raúl Camposano (Silicon Catalyst, entrepreneur, former Synopsys CTO and lecturer at Stanford, EE292A) and I continue our series on research ideas. As always, feedback welcome.

The Innovation

This month’s pick is Post-Silicon… Read More

2025 Outlook with Dr. Rui Tang of MSquare Technology

Tell us a little bit about yourself and your company.

I am Rui Tang, co-founder and VP of MSquare Technology. With a Ph.D. in Computer Engineering from Northeastern University and a master’s degree in management science and engineering from Stanford University, I bring over 23 years of experience in the IC industry. Prior to MSquare,… Read More

Synopsys Expands Hardware-Assisted Verification Portfolio to Address Growing Chip Complexity

Last week, Synopsys announced an expansion of their Hardware-Assisted Verification (HAV) portfolio to accelerate semiconductor design innovations. These advancements are designed to meet the increasing demands of semiconductor complexity, enabling faster and more efficient verification across software and hardware… Read More

How Synopsys Enables Gen AI on the Edge

Artificial intelligence and machine learning have undergone incredible changes over the past decade or so. We’ve witnessed the rise of convolutional neural networks and recurrent neural networks. More recently, the rise of generative AI and transformers. At every step, accuracy has been improved as depicted in the graphic… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era