In the current semiconductor design landscape, the design size and complexity of SoCs has grown to large extent with stable tools and technologies that can take care of integrating several IPs together. With that mammoth growth in designs, verification flows are evolving continuously to tackle the verification challenges … Read More

CEO Interview with Faraj Aalaei of CognichipFaraj Aalaei is a successful visionary entrepreneur with…Read More

CEO Interview with Faraj Aalaei of CognichipFaraj Aalaei is a successful visionary entrepreneur with…Read More Rethink Scoreboards to Supercharge AI-Era CPUsBy Dr. Thang Minh Tran, CEO/CTO Simplex Micro…Read More

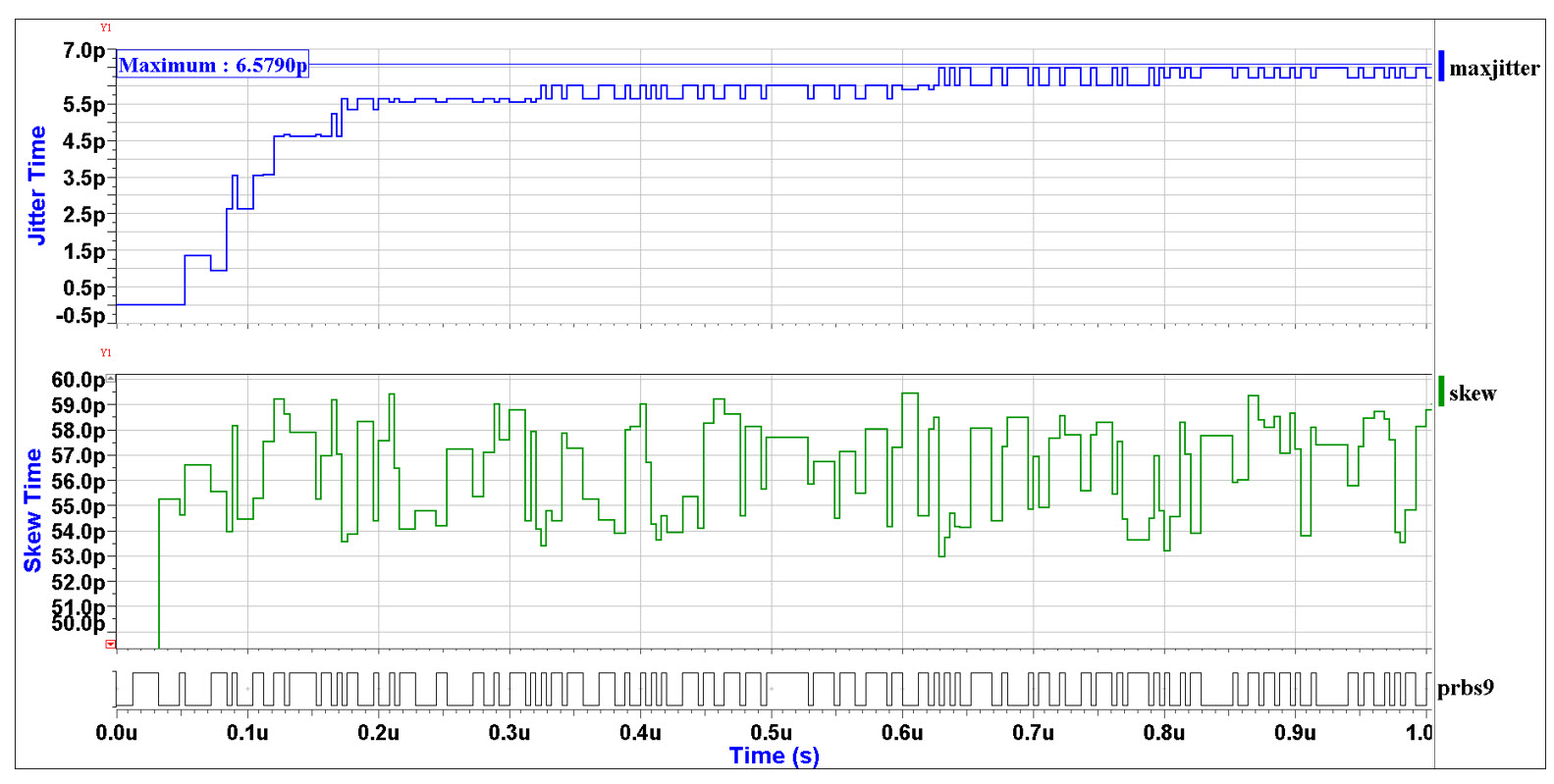

Rethink Scoreboards to Supercharge AI-Era CPUsBy Dr. Thang Minh Tran, CEO/CTO Simplex Micro…Read More Jitter: The Overlooked PDN Quality MetricBruce Caryl is a Product Specialist with Siemens EDA…Read More

Jitter: The Overlooked PDN Quality MetricBruce Caryl is a Product Specialist with Siemens EDA…Read More CEO Interview with Vamshi Kothur, of Tuple TechnologiesIt was my pleasure to meet with Vamshi…Read More

CEO Interview with Vamshi Kothur, of Tuple TechnologiesIt was my pleasure to meet with Vamshi…Read More Webinar – Power is the New Performance: Scaling Power & Performance for Next Generation SoCsWhat if you could reduce power and extend…Read More

Webinar – Power is the New Performance: Scaling Power & Performance for Next Generation SoCsWhat if you could reduce power and extend…Read MoreIntelligent Sensors

Wearables are clearly one of the hot areas of the Internet of Things (IoT). A big part of that market is sensors of one sort or another. Andes low power microprocessors are a good fit for this market which requires both 32 bit performance and ultra low power. Performance is needed since IoT by definition has internet access in some way… Read More

EDAC Update: Elections, Kaufman and More

I wrote recently about the EDAC mixer in Mountain View. Due to college basketball there won’t be one in March, the next one will be in April. Details later in the month.

The EDA Consortium (EDAC) is seeking nominations for the Board of Directors for the two-year term beginning May 29, 2014. Voting member companies are entitled… Read More

WordPress and EDA Software, How Do They Compare?

I first started using WordPress in 2008 after having written my own Content Management System (CMS) to build and manage web sites. WordPress is the number one CMS in the world, is just 10 years old, and is used by over 70 million users. What got me thinking about WordPress and EDA software companies was a recent book by Scott Burken, … Read More

Internet of Things and the Wearable Market

My wife and I drove to Southern California last week in search of information on the wearable computing market. After stops in Irvine, San Diego, and some play time in La Jolla we returned in time for the CASPA Symposium: “The Wearable Future: Moving Beyond the Hype; the Search for the Holy Grail and Practical Use Cases”… Read More

Semiconductor Strategy – From Productivity to Profitability

The semiconductor industry seems to be the most challenged in terms of cost of error; a delay of 3 months in product development cycle can reduce revenue by about 27% and that of 6 months can reduce it by almost half; competition is rife, pushing the products to next generation (with more functionality, low power, high performance,… Read More

IC Layout with Interactive or Batch DRC and LVS Results

IC designers have a long tradition of mixing and matching EDA tools from multiple vendors, mostly because they enjoy best-in-class tools, or they just purchased each EDA tool at a different time and asked for them to work together. Such is this case with IC layout tools from Silvacoand DRC/LVS tools from Mentor Graphics. Pawan Fangaria… Read More

Key Ingredients for ESL Power Modeling, Simulation, Analysis and Optimzations

There’s a French EDA company named DOCEA Powerthat is uniquely focused on power analysis at the ESL level and I had a chance to interview Ridha Hamza to get new insight on ESL design challenges and their approach. Ridha started out doing SRAM design at STMicroelectornics in the 1990’s, moved into the emerging field … Read More

On-Chip Clock Generation beyond Phase Locked Loop

Inside a today’s typical VLSI system, there are millions of electrical signals. They make the system perform what it is designed to do. Among those, the most important one is the clock signal. From an operational perspective, clock is the timekeeper of the electrical world inside the chip/system. From a structural perspective,… Read More

The (re)making of Arteris, 1-2-3

Success in a business with extended design-in cycles may look easy. In reality, there is a delicate balance between many factors. Some come to mind immediately: developing and releasing a good product in the first place; winning and keeping the right customers, not too few or too many; balancing investment between support and … Read More

Facing the Quantum Nature of EUV Lithography