In an era defined by complex chip architectures, ever-shrinking technology nodes and very demanding applications, Silicon Lifecycle Management (SLM) has become a foundational strategy for optimizing performance, reliability, and efficiency across the lifespan of a semiconductor device. Central to effective SLM are Process,… Read More

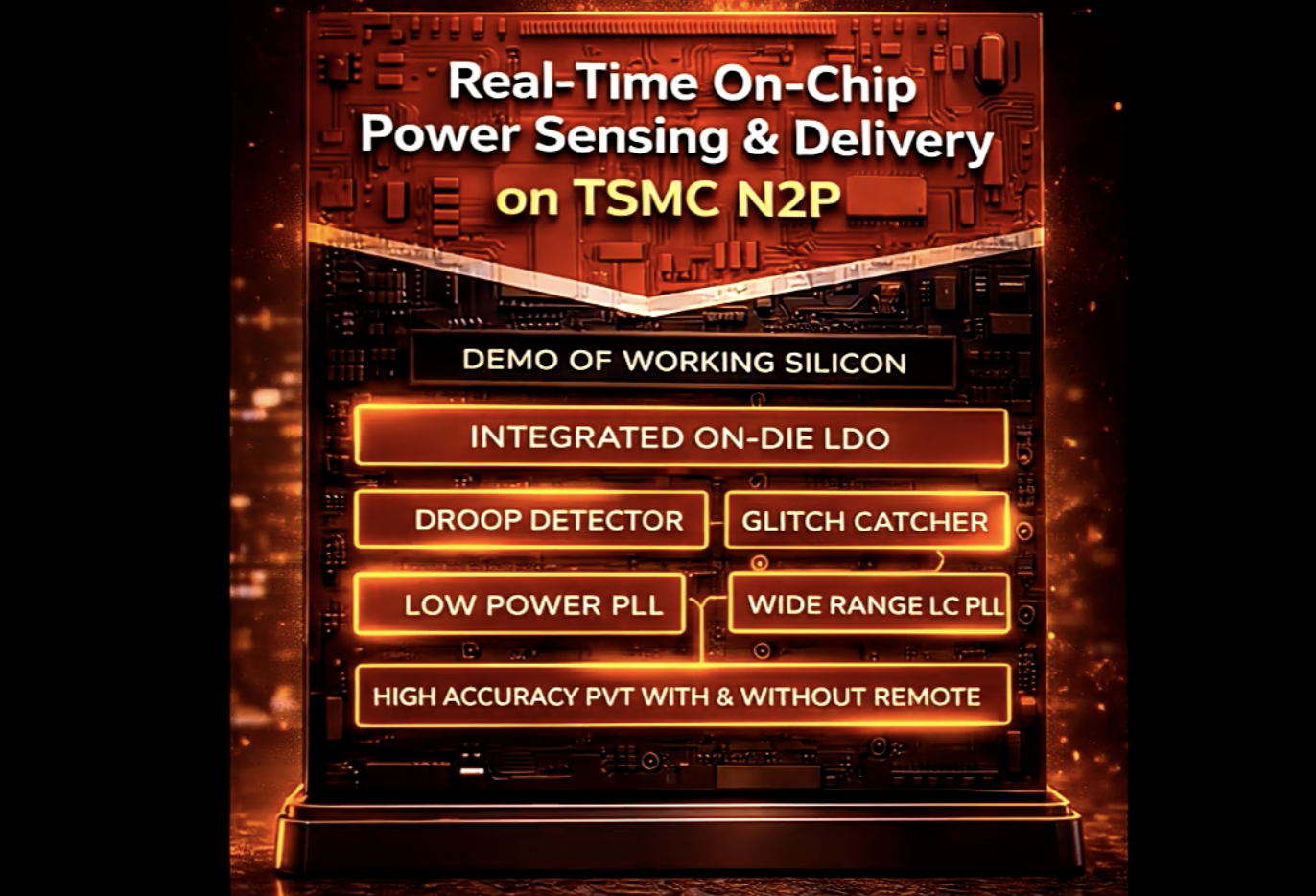

Analog Bits Demos Real-Time On-Chip Power Sensing and Delivery on N2P at the TSMC 2026 Technology SymposiumAnalog Bits has a way of stealing the…Read More

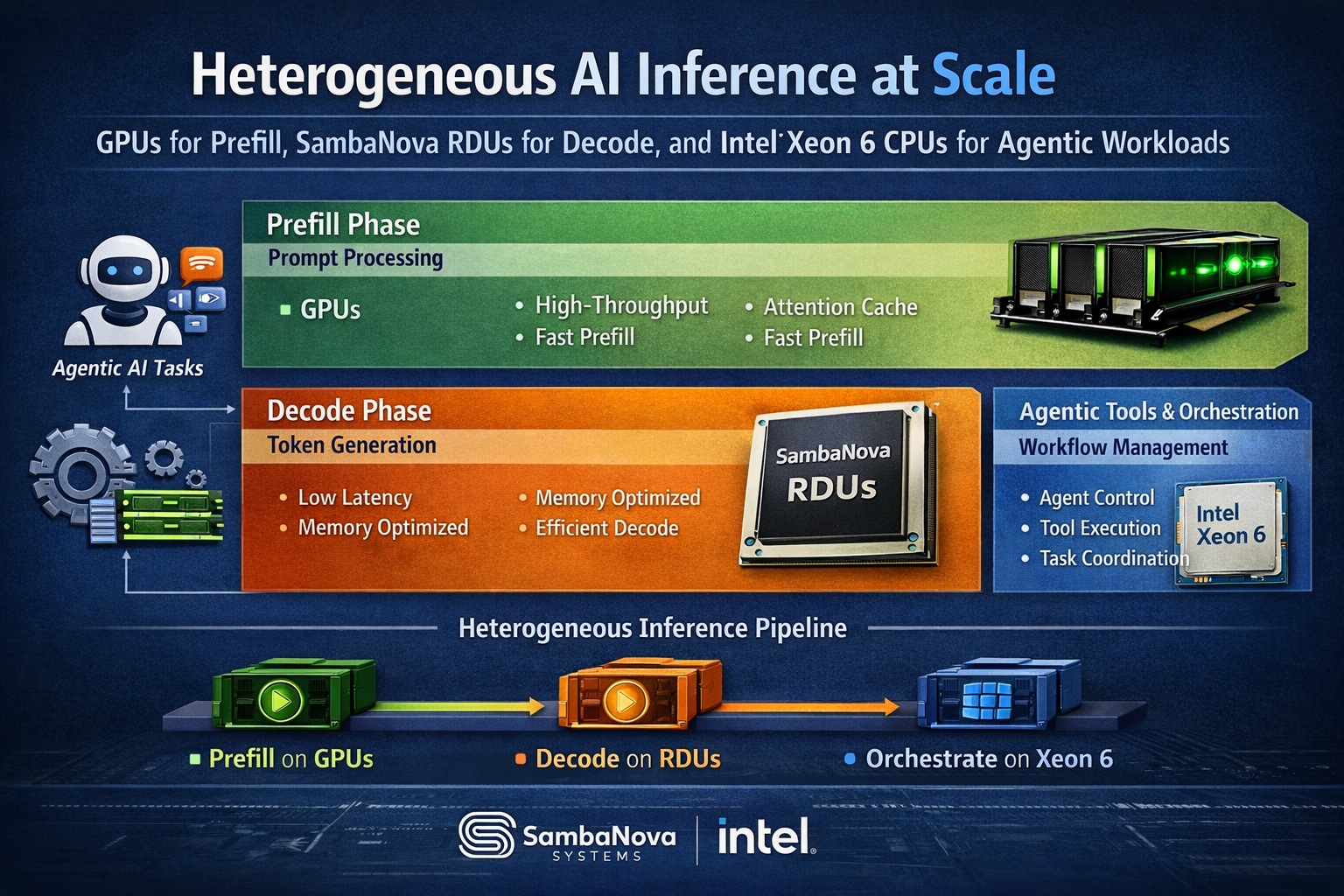

Analog Bits Demos Real-Time On-Chip Power Sensing and Delivery on N2P at the TSMC 2026 Technology SymposiumAnalog Bits has a way of stealing the…Read More Disaggregating LLM Inference: Inside the SambaNova Intel Heterogeneous Compute BlueprintSambaNova Systems and Intel have introduced a blueprint…Read More

Disaggregating LLM Inference: Inside the SambaNova Intel Heterogeneous Compute BlueprintSambaNova Systems and Intel have introduced a blueprint…Read More CEO Interview with Johan Wadenholt Vrethem of VoxoWith over two decades of experience bridging technology…Read More

CEO Interview with Johan Wadenholt Vrethem of VoxoWith over two decades of experience bridging technology…Read More TSMC to Elon Musk: There are no Shortcuts in Building Fabs!The opening of the TSMC 2026 earning call…Read More

TSMC to Elon Musk: There are no Shortcuts in Building Fabs!The opening of the TSMC 2026 earning call…Read More Speculation: Silicon’s Most Expensive CompulsionHow Time-Based Scheduling Reclaims Silicon Wasted by Speculative…Read More

Speculation: Silicon’s Most Expensive CompulsionHow Time-Based Scheduling Reclaims Silicon Wasted by Speculative…Read MoreTSMC Brings Packaging Center Stage with Silicon

The worldwide TSMC 2025 Technology Symposium recently kicked off with the first event in Santa Clara, California. These events typically focus on TSMC’s process technology and vast ecosystem. These items were certainly a focus for this year’s event as well. But there is now an additional item that shares the spotlight – packaging… Read More

TSMC 2025 Technical Symposium Briefing

At the pre-conference briefing, Dr. Kevin Zhang gave quite a few of us media types an overview of what will be highlighted at the 2025 TSMC Technical Symposium here in Silicon Valley. Since most of the semiconductor media are not local this was a very nice thing to do. I will be at the conference and will write more tomorrow after the … Read More

Perspectives from Cadence on Data Center Challenges and Trends

From my vantage point in the EDA foxhole it can be easy to forget that Cadence also has interests in much broader technology domains. One of these is in data center modeling and optimization, through their Cadence Reality Digital Twin Platform. This is an area in which they already have significant track record collaborating with… Read More

Semiconductor Tariff Impact

President Donald Trump has initially excluded semiconductors from his latest round of U.S. tariffs. However, he could put tariffs on semiconductors in the future. If tariffs are placed on semiconductors imported to the U.S., how would that affect U.S.-based semiconductor companies? The chart below shows U.S. semiconductor… Read More

Designing and Simulating Next Generation Data Centers and AI Factories

At NVIDIA’s recent GTC conference, a Cadence-NVIDIA joint session provided insights into how AI-powered innovation is reshaping the future of data center infrastructure. Led by Kourosh Nemati, Senior Data Center Cooling and Infrastructure Engineer from NVIDIA and Sherman Ikemoto, Sales Development Group Director from … Read More

CEO Interview with Dr. Michael Förtsch of Q.ANT

Dr. Michael Förtsch, CEO of Q.ANT, is a physicist and innovator driving advancements in photonic computing and sensing technologies. With a PhD from the Max Planck Institute for the Science of Light, he leads Q.ANT’s development of Thin-Film Lithium Niobate (TFLN) technology, delivering groundbreaking energy efficiency … Read More

Verifying Leakage Across Power Domains

IC designs need to operate reliably under varying conditions and avoid inefficiencies like leakage across power domains. But how do you verify that connections between IP blocks has been done properly? This is where reliability verification, Electrical Rule Checking (ERC) tools and dynamic simulations all come into play particularly… Read More

How Cadence is Building the Physical Infrastructure of the AI Era

At the 2025 NVIDIA GTC Conference, CEO Jensen Huang delivered a sweeping keynote that painted the future of computing in bold strokes: a world powered by AI factories, built on accelerated computing, and driven by agentic, embodied AI capable of interacting with the physical world. He introduced the concept of Physical AI—intelligence… Read More

TSMC’s Innovations in Physical Design for Semiconductor Scaling

In a 2017 ISPD presentation, TSMC Fellow LC Lu outlined critical challenges and innovations in physical design to sustain power, speed, and area scaling trends in semiconductors. As Moore’s Law faces economic hurdles, process-design co-optimization emerges as key to extending it. Lu emphasized application-optimized… Read More

Is Intel About to Take Flight?