Security will be an important topic at DAC this year. The hardware root of trust is the foundation of all security for complex systems implementing AI workloads. Thanks to new and sophisticated techniques the hardware root of trust is now vulnerable and must be protected. But adding deep security verification to existing design… Read More

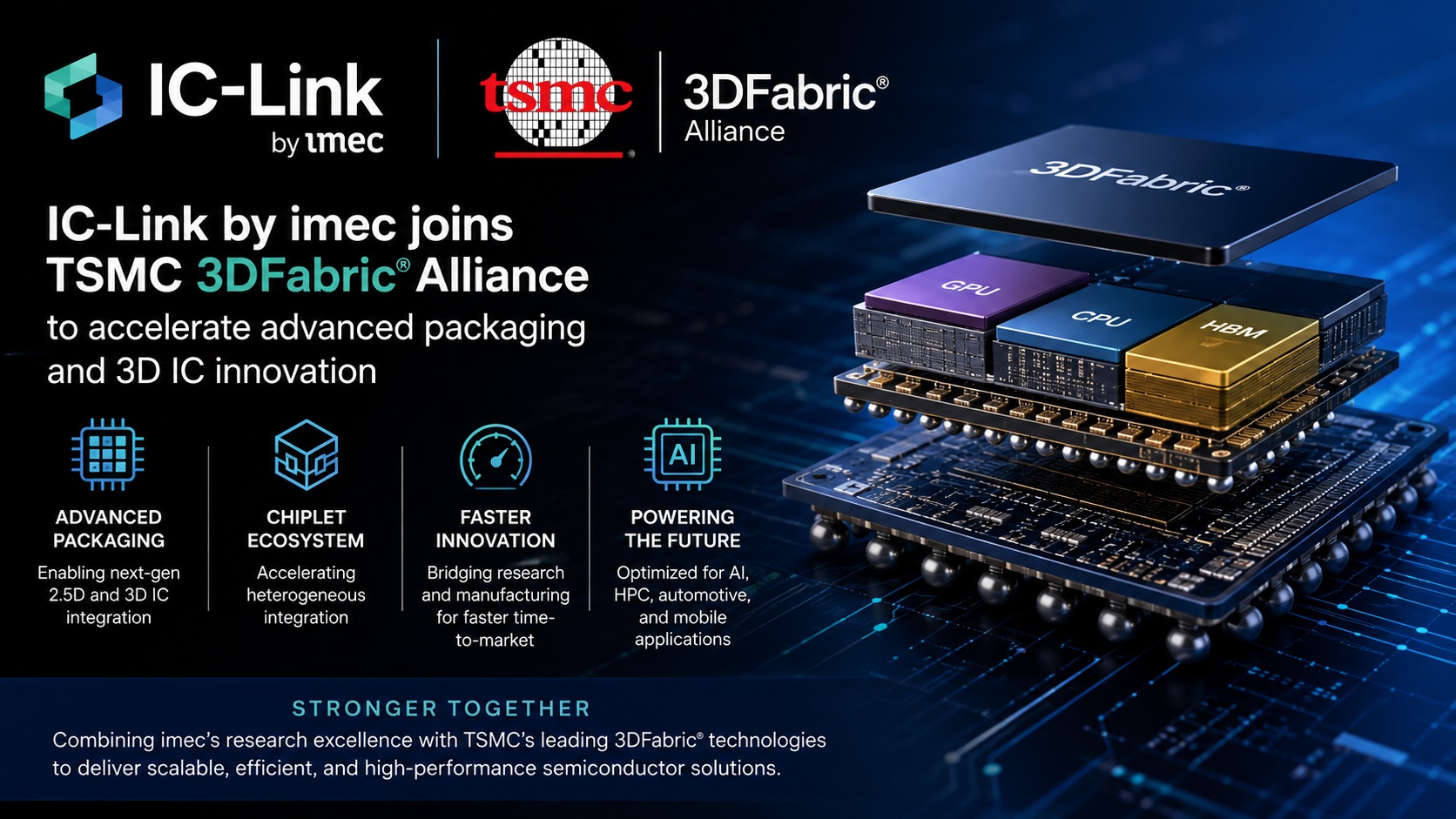

imec IC-Link and TSMC 3DFabric Alliance Expansion Signals New Era of System-Level Scalingimec announced that IC-Link by imec has joined…Read More

imec IC-Link and TSMC 3DFabric Alliance Expansion Signals New Era of System-Level Scalingimec announced that IC-Link by imec has joined…Read More From the Selfie to Samantha: The Next Trillion-Dollar BehaviorAt CES 2026, Samsung called it a “companion.”…Read More

From the Selfie to Samantha: The Next Trillion-Dollar BehaviorAt CES 2026, Samsung called it a “companion.”…Read More TSMC’s Record Tool Orders Hint at Another CapEx ShockwaveTSMC’s latest Board of Directors capital appropriation announcement…Read More

TSMC’s Record Tool Orders Hint at Another CapEx ShockwaveTSMC’s latest Board of Directors capital appropriation announcement…Read More CEO Interview with Nagesh Gupta of llmda.aiNagesh has built a career spanning multiple aspects…Read More

CEO Interview with Nagesh Gupta of llmda.aiNagesh has built a career spanning multiple aspects…Read MoreDefacto at the 2025 Design Automation Conference #62DAC

Defacto has been a leading provider of SoC integration tools for large-scale designs for years. Most major semiconductor companies already use their solutions, and several customers will be presenting how they leverage the Defacto solution (SoC Compiler) at the upcoming DAC conference.

LUBIS EDA at the 2025 Design Automation Conference #62DAC

At the Design Automation Conference (DAC) 2025 in San Francisco, LUBIS EDA returns as an exhibitor to showcase its latest innovations in formal verification automation, helping semiconductor teams move faster and with more confidence through the most complex verification challenges.

LUBIS EDA is a fast-growing EDA startup… Read More

Legacy IP Providers Struggle to Solve the NPU Dilemna

At Quadric we do a lot of first-time introductory visits with prospective new customers. As a rapidly expanding processor IP licensing company that is starting to get noticed (even winning IP Product of the Year!) such meetings are part of the territory. Which means we hear a lot of similar sounding questions from appropriately… Read More

A Novel Approach to Future Proofing AI Hardware

There is a built-in challenge for edge AI intended for long time-in-service markets. Automotive applications are the obvious example, while aerospace and perhaps medical usage may impose similar demands. Support for the advanced AI methods we now expect – transformers, physical and agentic AI – is not feasible without dedicated… Read More

Mixel at the 2025 Design Automation Conference #62DAC

Mixel, Inc., a leading provider of mixed-signal interface IP, will exhibit at booth #2616 at Design Automation Conference (DAC) 2025 on June 23-25. The company will demonstrate its latest customer demos featuring Mixel’s MIPI PHY IP and LVDS IP. Mixel’s customers include many of the world’s largest semiconductors and system… Read More

Advancements in 3D Stacked IGZO 2T0C DRAM for Computing-in-Memory Applications

In the rapidly evolving field of artificial intelligence (AI), the demand for efficient data processing has exposed limitations in traditional memory technologies. The paper “3D Stacked IGZO 2T0C DRAM Array with Multibit Capability for Computing in Memory Applications,” published in Science Advances on May… Read More

Analog Bits at the 2025 Design Automation Conference #62DAC

Analog Bits attends a lot of events. I know because I see them a lot in my travels. Lately, the company has been stealing the show with cutting-edge analog IP on a broad range of popular nodes and a strategy that will change the way design is done. Analog Bits is quietly rolling out a new approach to system design. One that delivers a holistic… Read More

SoC Front-end Build and Assembly

Modern SoCs can be complex with hundreds to thousands of IP blocks, so there’s an increasing need to have a front-end build and assembly methodology in place, eliminating manual steps and error-prone approaches. I’ve been writing about an EDA company that focuses on this area for design automation, Defacto Technologies, and … Read More

Siemens EDA Outlines Strategic Direction for an AI-Powered, Software-Defined, Silicon-Enabled Future

In a keynote delivered at this year’s Siemens EDA User2User event, CEO Mike Ellow presented a focused vision for the evolving role of electronic design automation (EDA) within the broader context of global technology shifts. The session covered Siemens EDA’s current trajectory, market strategy, and the changing landscape … Read More

Crossing the Yield Cliff: IDP V6 and the Future of Manufacturing Forecasting