An interesting thing happened during the driving tour of the GlobalFoundries Fab 8 in Malta, NY. We happened by an old structure with quite a bit of history. As it turns out, the “Malta Test Station”, a former US Army fuel and explosives testing facility, was the actual birthplace of the United States’ Space & Missile programs.… Read More

Captain America: Can Elon Musk Save America's Chip Manufacturing Industry?Intel has posted three consecutive years of falling…Read More

Captain America: Can Elon Musk Save America's Chip Manufacturing Industry?Intel has posted three consecutive years of falling…Read More WEBINAR: Reclaiming Clock Margin at 3nm and BelowAt 3nm and below, clock networks have quietly…Read More

WEBINAR: Reclaiming Clock Margin at 3nm and BelowAt 3nm and below, clock networks have quietly…Read More WEBINAR: HBM4E Advances Bandwidth Performance for AI TrainingThe rapid proliferation of LLMs and other AI…Read More

WEBINAR: HBM4E Advances Bandwidth Performance for AI TrainingThe rapid proliferation of LLMs and other AI…Read More Siemens Wins Best in Show Award at Chiplet Summit and Targets Broad 3D IC Design EnablementThe recent Chiplet Summit in Santa Clara was…Read More

Siemens Wins Best in Show Award at Chiplet Summit and Targets Broad 3D IC Design EnablementThe recent Chiplet Summit in Santa Clara was…Read More Siemens Fuse EDA AI Agent Releases to Orchestrate Agentic Semiconductor and PCB DesignThough terminology sometimes get fuzzy, consensus holds that…Read More

Siemens Fuse EDA AI Agent Releases to Orchestrate Agentic Semiconductor and PCB DesignThough terminology sometimes get fuzzy, consensus holds that…Read MoreGlobalFoundries Visit – Part 1 – It’s All About Execution

Fabless companies and the need for foundries

The success of fabless semiconductor companies is well documented with companies such as Qualcomm, Broadcom, MediaTek, AMD, Avago and others selling semiconductors made using the fabless model (see Fabless: The Transformation of the Semiconductor Industry by Daniel Nenni and … Read More

What Makes Us Indecisive?

An indecision is actually a very bad decision. It is an implicit decision for the status quo. It is worse than an explicit decision regardless of how bad that decision turns out to be. In my experience, our indecisiveness is caused by various reasons involving trade-offs.… Read More

Moore’s Law Linear Approximation and Mathematical Analysis!

Respected Gordon Moore has given the real computing power to the world and Respected Stephen Hawking’s work from past many years has given the reality of physics and mathematics to the universe. We can imagine the shrinking and intelligence in computing due to the real evolution of semiconductor technology. The process… Read More

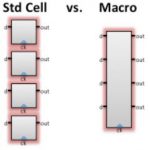

The Revenge of Microprocessor Design: The Return of the Macro

(Two Star Wars™ allusions in one title – eat your heart out George Lucas.) Most of us are comfortable with the idea that you design more or less whatever you want in RTL and let the synthesis tool pick logic gates to implement that functionality. Sure it may need a little guidance here and there but otherwise synthesis is more or less … Read More

China Further Expands Its Influence in Semiconductor Industry

For the fourth consecutive year, China’s semiconductor consumption growth far exceeded worldwide market growth. At the end of 2014, the country had a record 56.6% of the global semiconductor consumption market.

China’s semiconductor consumption grew by 12.6% in 2014, exceeding the worldwide chip market growth of 9.8%. To … Read More

Moore’s Law and Silicon Forest

When I first moved to Oregon in 1978 the largest industry was forestry, but then the endangered Spotted Owl was found and that put an end to many forestry companies and decimated the economy of many rural cities. Strangely enough it turns out that the Spotted Owl was found in great numbers across multiple states, so it never should’ve… Read More

ARM TechCon 2015 Preview!

Of all the live events I attend ARM TechCon is one of my favorites. The keynotes are always very good but the real meat of the conference is who attends because that is who the content is specifically developed for:… Read More

Why Gemini 2.0 is tailored for tomorrow’ SoC designs?

You probably have seen many times this graphic showing that the number of IP blocks has exploded, going from a few dozens in SoC designed in 65 nm to 120 if not more for last generation SoC targeting 16FF or 10FF. This graphic is very good at synthesizing the raw IP count, but it doesn’t tell you about another strong trend: more agents … Read More

Pushing on AXI-connected IP in FPGAs

Success stories are great. Reading how someone uses a product contributes much more insight than reading about a product. Last month we had a teaser for a presentation by Wave Semiconductor; this month, we have the slides showing how they are using FPGA-based prototyping, AXI transactions, and DPI to speed up development.

First,… Read More

Chemical Origins of Environmental Modifications to MOR Lithographic Chemistry