It seems of late like there is an unlimited thirst for GPU performance at the right power efficiency. Whether it is deep learning, object recognition, artificial intelligence, simulations, VR or AR, the industry desperately needs GPU improvements. Many within the graphics industry would agree that a new era of graphics performance… Read More

Samtec’s Strong Presence at embedded world 2026The embedded world Exhibition & Conference recently concluded.…Read More

Samtec’s Strong Presence at embedded world 2026The embedded world Exhibition & Conference recently concluded.…Read More Webinar – How to Reclaim Margin in Advanced NodesThis informative webinar discusses a significant issue that…Read More

Webinar – How to Reclaim Margin in Advanced NodesThis informative webinar discusses a significant issue that…Read More Alchip’s Leadership in ASIC Innovation: Advancing Toward 2nm Semiconductor TechnologyAlchip Technologies has recently reported significant progress in…Read More

Alchip’s Leadership in ASIC Innovation: Advancing Toward 2nm Semiconductor TechnologyAlchip Technologies has recently reported significant progress in…Read More CapEx Up for Foundry, MemorySemiconductor Intelligence estimates total semiconductor industry capital spending…Read More

CapEx Up for Foundry, MemorySemiconductor Intelligence estimates total semiconductor industry capital spending…Read MoreHow to handle petabyte-scale traffic growth?

If you search the web for IP traffic growth, you will find many graphics, but the common result is that IP traffic is growing with high CAGR for many years and will again continue to grow with such high CAGR for the next five years. For example the global mobile data traffic is expected to grow with 53% CAGR 2015-2020… even if the smartphone… Read More

Emerging Smartphone Display Insights from Patents

US201403549 illustrates a display that includes the multifunctional pixels. Each multifunctional pixel can include several display areas as well sensors. Combining visual display technology with sensors provides the touchscreen operation by use of a finger, stylus or other object positioned on or near the visual display,… Read More

To EUV, or not to EUV, that is the question!

SPIE is next week so if you would like to meet me in person that is where I will be. SPIE is the big lithography and patterning conference for semiconductor professionals. Since I work with the foundries during my day job, SPIE is an important conference. SemiWiki blogger Scott Jones will also be there. During the day Scott does semiconductor… Read More

Why Apple’s Fight is Fruitless!

The article suggested by LinkedIn is titled “Should Apple fight a court order to unencrypt iPhones? #unlockiPhone”. However, my question is this, why didn’t the FBI just go to the NSA for what they needed? Why didn’t the FBI just hire the latest hacker who was able to hack the iphone and give him the same deal other hackers… Read More

New CEVA X baseband architecture takes on multi-RAT

What we think of as a “baseband processor” for cellular networks is often comprised of multiple cores. Anecdotes suggest to handle the different signal processing requirements for 2G, 3G, and 4G networks, some SoC designs use three different DSPs plus a control processor such as an ARM core. That’s nuts. What is the point of having… Read More

Tesla’s Secret Weapon!

Some CEO’s make things look easy and appear to enjoy their work. CEO’s like Richard Branson and Warren Buffet come to mind. These are guys that clearly enjoy what they are doing and, as a result, make everything they do look effortless and fun.

Tesla’s Chairman and CEO, Elon Musk, is another one of these types. There is an impishness… Read More

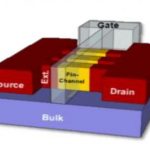

FinFETs, Power Integrity and Chip/Package Co-design

FinFETs have brought a lot of good things to design – higher performance, higher density and lower leakage power – promising to extend Moore’s law for a least a while longer. But inevitably with new advances come new challenges, especially around optimizing for power integrity in these designs.

One of these challenges is… Read More

Internet of Things- Keeping the Best Things First

The growth of the Internet of Things and embedded and wearable devices—will have widespread and beneficial effects by 2025. In all of these exponentially-growing technologies — artificial intelligence, robotics, nanomaterials, biotech, bioinformatics, quantum computing, Internet of everything — these … Read More

Exploring USB Type-C DRP to USB Type-C DFP connection using USB C-Thru

In a USB Type-C environment configuration process between a DRP and a DFP is as follows:

- DRP to DFP attach/detach detection

- Plug orientation detection

- Initial DRP to DFP and power relationship detection

- USB Type-C VBus current detection and usage

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center