Everspin’s recent fireside chat, moderated by Robert Blum of Lithium Partners, offered a crisp look at how the company is carving out a durable niche in non-volatile memory. CEO Sanjeev Agrawal’s core message was simple: MRAM’s mix of speed, persistence, and robustness lets it masquerade as multiple memory classes, data-logging,… Read More

Enabling Next-Generation AI Through Advanced Packaging and 3D Fabric IntegrationThe rapid rise of artificial intelligence is fundamentally…Read More

Enabling Next-Generation AI Through Advanced Packaging and 3D Fabric IntegrationThe rapid rise of artificial intelligence is fundamentally…Read MoreA Principled AI Path to Spec-Driven Verification

I have seen a flood of verification announcements around directly reading product specs through LLM methods, and from there directly generating test plans and test suite content to drive verification. Conceptually automating this step makes a lot of sense. Carefully interpreting such specs even today is a largely manual task,… Read More

Exploring the Latest Innovations in MIPI D-PHY and MIPI C-PHY

The white paper “Exploring the Latest Innovations in MIPI D-PHY and MIPI C-PHY” details the latest developments in these two critical high-speed interface technologies, highlighting how they evolve to meet modern demands in camera and display systems across automotive, industrial, healthcare, and XR applications.… Read More

448G: Ready or not, here it comes!

The march toward higher-speed networking continues to be guided by the same core objectives as has always been : increase data rates, lower latency, improve reliability, reduce power consumption, and maintain or extend reach while controlling cost. For the next generation of high-speed interconnects, these requirements … Read More

Should the US Government Invest in Intel?

“Most companies don’t die because they are wrong; most die because they don’t commit themselves. They fritter away their valuable resources while attempting to make a decision. The greatest danger is standing still.” Andy Grove’s Only the Paranoid Survive, first published in 1996.

Looking back 20 years, we all know this… Read More

PDF Solutions and the Value of Fearless Creativity

PDF Solutions has been around for over 30 years. The company began with a focus on chip manufacturing and yield. Since the beginning, PDF Solutions anticipated many shifts in the semiconductor industry and has expanded its impact with enhanced data analytics and AI. Today, the company’s impact is felt from design to manufacturing,… Read More

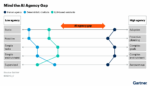

Gartner Top Strategic Technology Trends for 2025: Agentic AI

Agentic AI refers to goal-driven software entities—“digital coworkers”—that can plan, decide, and act on an organization’s behalf with minimal supervision. Unlike classic chatbots or coding assistants that respond only to prompts, agentic systems combine models (e.g., LLMs) with memory, planning, tools/APIs, sensing,… Read More

AMAT China Collapse and TSMC Timing Trimming

– AMAT has OK Q but horrible guide as China & Leading edge drop

– China finally chokes on indigestion & export issues -$500M hit

– TSMC trims on fab timing causing leading edge to slow -$500M hit

– Cycle which had slowed to single digits has rolled over to negative

AMAT guides down for big miss on Q4

… Read MoreCEO Interview with Russ Garcia with Menlo Micro

Russell (Russ) Garcia is a veteran technology executive with over 30 years of leadership experience in semiconductors, telecommunications, and advanced electronics. As CEO of Menlo Microsystems, he has led the commercialization of disruptive MEMS switch technology across RF, digital, and power systems.

Previously, Russ… Read More

Video EP9: How Cycuity Enables Comprehensive Security Coverage with John Elliott

In this episode of the Semiconductor Insiders video series, Dan is joined by John Elliott, security applications engineer from Cycuity. With 35 years of EDA experience, John’s current focus is on security assurance of hardware designs.

John explains the importance of security coverage in the new global marketplace. He describes… Read More

Solving the EDA tool fragmentation crisis