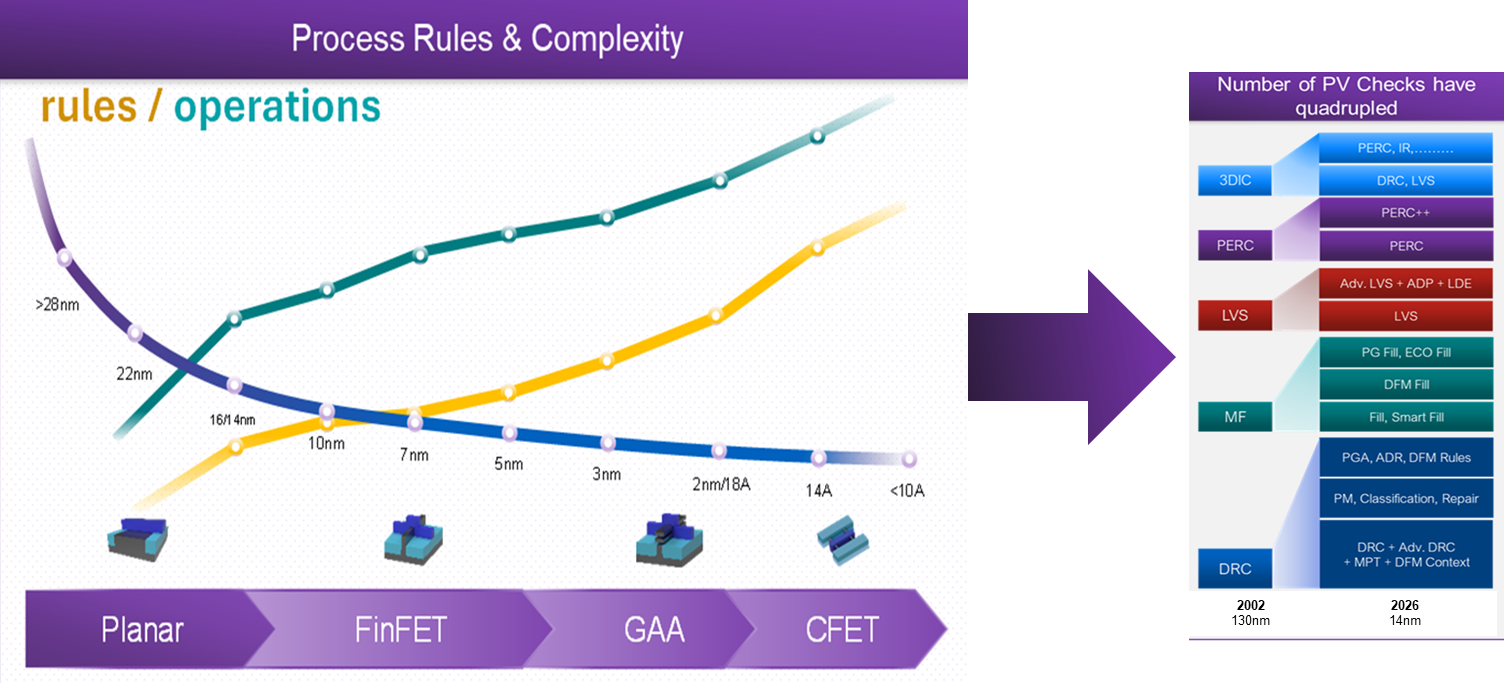

Everyone knows design complexity is exploding. What used to be difficult is now bordering on impossible. While design and verification challenges occupy a lot of the conversation, the problem is much bigger than this. The new design and manufacturing challenges of 3D innovations and the need to coordinate a much more complex … Read More

Carbon in the Age of AI Chips: What the Semiconductor Industry Needs to Know This Earth DayStephen Russell: Senior Technical Fellow, TechInsights Every April,…Read More

Carbon in the Age of AI Chips: What the Semiconductor Industry Needs to Know This Earth DayStephen Russell: Senior Technical Fellow, TechInsights Every April,…Read More How to Overcome the Advanced Node Physical Verification BottleneckIt is well-known that advanced semiconductor process technology…Read More

How to Overcome the Advanced Node Physical Verification BottleneckIt is well-known that advanced semiconductor process technology…Read More proteanTecs at Chiplet Summit – Changing the Game for Health & Performance Monitoring of ChipletsThe recent Chiplet Summit 2026 was a great…Read More

proteanTecs at Chiplet Summit – Changing the Game for Health & Performance Monitoring of ChipletsThe recent Chiplet Summit 2026 was a great…Read MoreRevolutionizing Processor Design: Intel’s Software Defined Super Cores

In the ever-evolving landscape of computing, Intel’s patent application for “Software Defined Super Cores” (EP 4 579 444 A1) represents a groundbreaking approach to enhancing processor performance without relying solely on hardware scaling. Filed in November 2024 with priority from a U.S. application… Read More

TSMC’s 2024 Sustainability Report: Pioneering a Greener Semiconductor Future

TSMC, the world’s most trusted semiconductor foundry, released its 2024 Sustainability Report, underscoring its commitment to embedding environmental, social, and governance principles into its operations. Founded in 1987 and headquartered in Hsinchu Science Park, TSMC employs 84,512 people globally and operates… Read More

Intel’s Commitment to Corporate Responsibility: Driving Innovation and Sustainability

Introduction by Lip-BU Tan:

I’m an engineer at heart. Nothing motivates me more than solving hard problems. Our teams across Intel are driven by this same mindset—inspired by the power of technology to enable new solutions to our customers’ toughest challenges.

I fundamentally believe this will be a catalyst for innovation throughout… Read More

CEO Interview with Rabin Sugumar of Akeana

Rabin Sugumar was Distinguished Engineer and Chief Architect at Marvell/Cavium and built and led the architecture group for the ThunderX Arm server processor line. Most recently he led the architecture of the ThunderX3 processor, which had industry leading single thread performance and socket level performance at time of … Read More

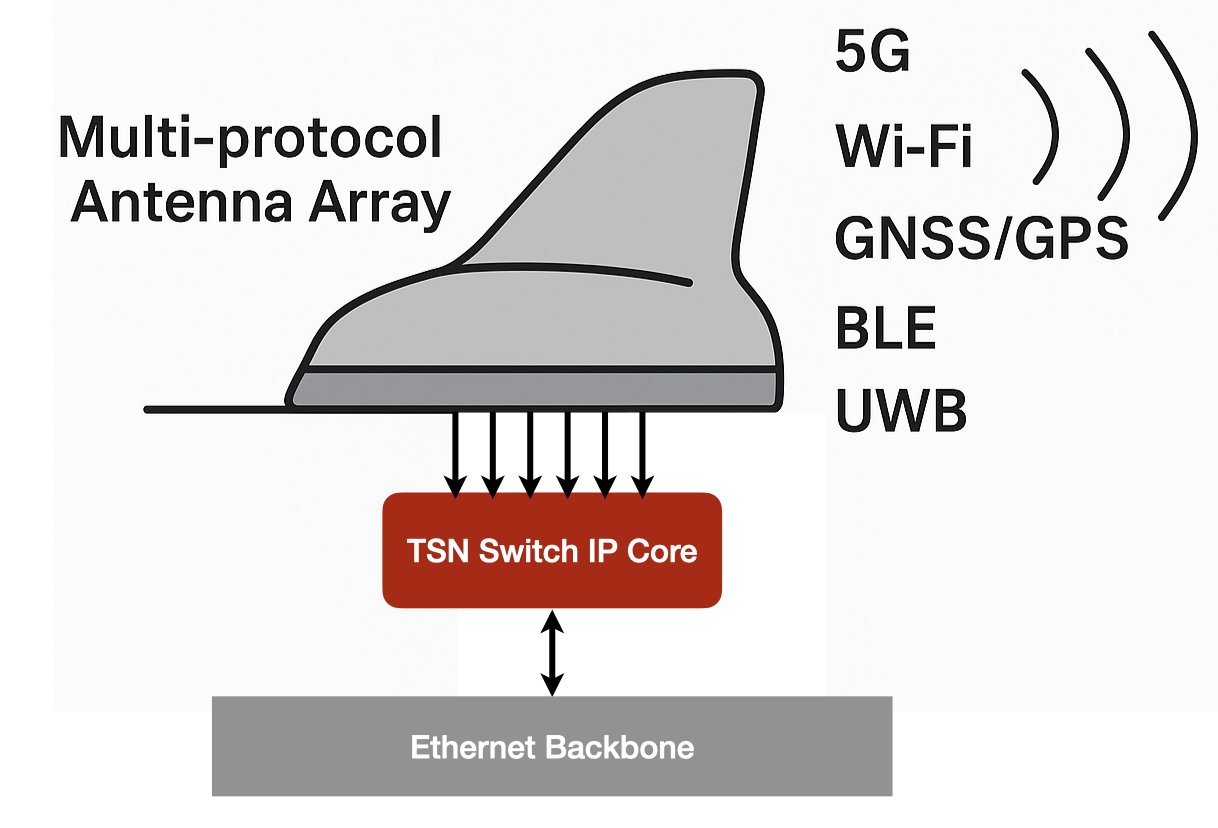

RANiX Employs CAST’s TSN IP Core in Revolutionary Automotive Antenna System

This press release from CAST announces a significant collaboration with RANiX Inc., highlighting the integration of CAST’s TSN Switch IP core into RANiX’s new Integrated Micro Flat Antenna System (IMFAS) SoC. This development underscores the growing adoption of Time-Sensitive Networking (TSN) in the automotive… Read More

Podcast EP306: The Challenges of Advanced AI Data Center Design with Josue Navarro

Dan is joined by Josue Navarro, product marketing engineer for Microchip’s dsPIC business unit. He began his career as a process engineer at Intel and has since transitioned into product marketing with Microchip Technology where he supports customers developing system designs utilizing Microchip’s Digital Signal … Read More

Cadence’s Strategic Leap: Acquiring Hexagon’s Design & Engineering Business

In a bold move that underscores the accelerating convergence of electronic design automation (EDA) and mechanical engineering, Cadence Design Systems announced its agreement to acquire Hexagon AB’s Design & Engineering (D&E) business for approximately €2.7 billion, equivalent to about $3.16 billion. This… Read More

TSMC 2025 Update: Riding the AI Wave Amid Global Expansion

Welcome to the second half of a very exciting year in semiconductors. While Intel and Samsung Foundry have made quite a few headlines, TSMC continues to execute flawlessly at 3nm and 2nm. With the TSMC OIP Ecosystem Forums starting later this month let’s take a look at how we got to where we are today.

Alchip’s 3DIC Test Chip: A Leap Forward for AI and HPC Innovation

Today Alchip Technologies, a Taipei-based leader in high-performance and AI computing ASICs, announced a significant milestone with the successful tape-out of its 3D IC test chip. This achievement not only validates Alchip’s advanced 3D IC ecosystem but also positions the company as a frontrunner in the rapidly evolving field… Read More

Is Intel About to Take Flight?