A robust, proven library of IP is a critical enabler for the entire semiconductor ecosystem. Without it, ASIC design is pretty much impossible, given time-to-market pressures. Said another way, designing IP for your next chip simply doesn’t fit the schedule – most teams have barely enough time to integrate and validate pre-existing… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data CenterAt the TERAFAB launch event in Austin on…Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data CenterAt the TERAFAB launch event in Austin on…Read More Synopsys Advances Hardware Assisted Verification for the AI EraAt the 2026 Synopsys Converge Event, Synopsys announced…Read More

Synopsys Advances Hardware Assisted Verification for the AI EraAt the 2026 Synopsys Converge Event, Synopsys announced…Read More Chemical Origins of Environmental Modifications to MOR Lithographic ChemistryIn the pursuit of advanced extreme ultraviolet (EUV)…Read More

Chemical Origins of Environmental Modifications to MOR Lithographic ChemistryIn the pursuit of advanced extreme ultraviolet (EUV)…Read More Post-Silicon Validating an MMU. Innovation in VerificationSome post-silicon bugs are unavoidable, but we’re getting…Read More

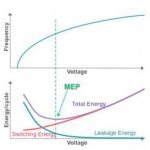

Post-Silicon Validating an MMU. Innovation in VerificationSome post-silicon bugs are unavoidable, but we’re getting…Read MoreIntegrated Power Management IP to Decrease Power and Cost

This blog is the synthesis of a white paper “New Power Management IP Solution from Dolphin Integration can dramatically increase SoC Energy Efficiency”, which can be found on Dolphin Integration web site.

The power consumption generated by complex chips was not a real issue when the system could be simply plugged in the wall to … Read More

Beyond DRC and LVS, why Reliability Verification is used by Foundries

Reliability of ICs isn’t a new thing, because back in 1980 I was investigating why a DRAM chip using 6um technology was having yield loss due to electromigration effects. I recall looking through a microscope at a DRAM layout and slowly ramping up the Vdd level then suddenly the shiny aluminum interconnect started to change… Read More

Webinar: Multicycle Vectorless Dynamic IR Signoff for Near 100 Percent Coverage

Check this webinar out – Mediatek will share a novel approach to early IR drop estimation. Competition in system design has become even more intense because potential markets are huge and there are more players with deep pockets chasing those markets. Wherever you are in those value chains, you want to shift everything left to accelerate… Read More

Facebook and WhatsApp are not just flawed they are downright dangerous

Facebook’s woes are spreading globally, first from the U.S., then to Europe and now in Asia. A study by researchers at the University of Warwick in the U.K. has conclusively established that Facebook has been fanning the flames of hatred in Germany. The study found that the rich and the poor, the educated and the uneducated, and those… Read More

UMC and GF or Samsung and GF?

One of the interesting rumors in Taiwan last week was the possibility that UMC and GF will do a deal to merge or UMC will buy some GF fabs. I have talked to quite a few industry experts about it and will talk to more this week at the GSA US Executive Forum (more at the end). The US Executive Forum is what they call a C Level event which means it… Read More

Mentor Rise and Fall

This is the fifteenth in the series of “20 Questions with Wally Rhines”

During 1980 and 1981, three companies, Daisy, Mentor and Valid were founded. Daisy and Valid attacked the computer automated design business with custom hardware workstations plus software to provide the unique capabilities required by engineers.… Read More

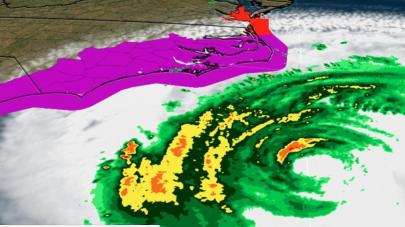

OnStar Missing the Florence Boat

Here we go again. A hurricane is closing in on the U.S. East Coast and General Motors’ OnStar connected car team – now part of something called Global Connected Consumer Experience – is AWOL.

While mandatory evacuations have been ordered and two-way highway connections to the coast have been switched to single… Read More

Easing Your Way into Portable Stimulus

The Portable Stimulus Standard (PSS) was officially released at DAC this year. While it will no doubt continue to evolve, for those who were waiting on the sidelines, it is officially safe to start testing the water. In fact it’s probably been pretty safe for a while; vendors have had solutions out for some time and each is happy to … Read More

Fuzzing on Automotive Security

The ECU. That was the service department prognosis on the root cause of thealways-on air bag safety light on my immaculate car. Ten years ago the cost for its replacement with after market part was at par with getting a new iPhone 8. Today, we could get four units for the same price and according to data from several research companies,… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center