I came across a report on the 100 most promising AI start-ups. The report claimed that CBInsights had “selected the 100 most promising AI start-ups from a pool of 3K+ companies based on several factors …” Wait, what … 3K+ companies!?!? This was a stunning reminder of the sheer magnitude of what is shaping up to be a veritable tsunami… Read More

Samtec’s Strong Presence at embedded world 2026The embedded world Exhibition & Conference recently concluded.…Read More

Samtec’s Strong Presence at embedded world 2026The embedded world Exhibition & Conference recently concluded.…Read More Webinar – How to Reclaim Margin in Advanced NodesThis informative webinar discusses a significant issue that…Read More

Webinar – How to Reclaim Margin in Advanced NodesThis informative webinar discusses a significant issue that…Read More Alchip’s Leadership in ASIC Innovation: Advancing Toward 2nm Semiconductor TechnologyAlchip Technologies has recently reported significant progress in…Read More

Alchip’s Leadership in ASIC Innovation: Advancing Toward 2nm Semiconductor TechnologyAlchip Technologies has recently reported significant progress in…Read More CapEx Up for Foundry, MemorySemiconductor Intelligence estimates total semiconductor industry capital spending…Read More

CapEx Up for Foundry, MemorySemiconductor Intelligence estimates total semiconductor industry capital spending…Read MoreThe Coming Tsunami in Multi-chip Packaging

The pace of Moore’s Law scaling for monolithic integrated circuit density has abated, due to a combination of fundamental technical challenges and financial considerations. Yet, from an architectural perspective, the diversity in end product requirements continues to grow. New heterogeneous processing units are being… Read More

HBM or CDM ESD Verification – You Need Both

In the realm of ESD protection, Charged Device Model (CDM) is becoming the biggest challenge. Of course, Human Body Model (HBM) is still essential, and needs to be used when verifying chips. However, a number of factors are raising the potential losses that CDM events can cause relative to HBM. These factors fall into two categories:… Read More

Konica Minolta Talks About High-Level Synthesis using C++

In the early days of chip design circa 1970’s the engineers would write logic equations, then manually reduce that logic using Karnaugh Maps. Next, we had the first generation of logic synthesis in the early 1980’s, which read in a gate-level netlist, performed logic reduction, then output a smaller gate-level netlist.… Read More

WEBINAR: GPU-Powered SPICE – The Way Forward for Analog Simulation

Several years ago, I was a consultant to a company called Gauda, Inc. I enjoyed working with Gauda as the technology was interesting. On June 3, 2014, Gauda, Inc. was acquired by D2S, Inc. so their technology lives on. Gauda was focused on optical proximity correction (OPC) and optical proximity verification solutions utilizing… Read More

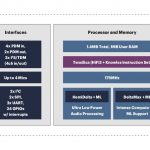

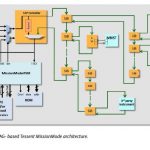

Smart Hearing is Heating Up

A lot of the attention in intelligent systems is on object detection in still or video images but there’s another very active area, in smart audio. Amazon and Google smart speakers may be the best-known applications but there are more obvious (and perhaps less novelty-driven) applications in enhancing the hearing devices we already… Read More

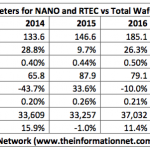

The Nanometrics – Rudolph Technology Merger: What Was Nanometrics Thinking?

On June 24, 2019, Nanometrics and Rudolph Technology announced they will combine in an all-stock merger of equals transaction. The companies say the combination increases the SAM (served available market) opportunity to approximately $3B.

This article attempts to analyze the two companies in their different business segments,… Read More

Automotive Market Pushing Test Tool Capabilities

It’s easy to imagine that the main impetus for automotive electronics safety standards like ISO 26262 is the emergence of autonomous driving technology. However, even cars that do not offer this capability rely heavily on electronics for many critical systems. These include engine control, braking, crash sensors, and stability… Read More

Early IP Block Error Detection is Critical!

The rising complexity of modern SoC designs, as enabled by progressing manufacturing technology, leads to an increasing validation challenge as the only way to manage complexity increase is by re-using more pre-designed IP blocks. These IP-blocks are provided by various suppliers such as a foundry partner, internal design… Read More

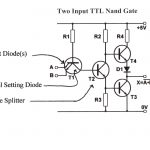

Texas Instruments and the TTL Wars

The “20 Questions with John East” series continues

Most people in the IC business understand very well that TTL products dominated our industry for 30 years or so. They’ll also probably know that TI was the king of TTL. But, if you ask those people what TTL is, most won’t have any idea. If you’re one of those people, rest easy. … Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center