You know that a technology is becoming a trend to watch when the Economist writes a piece on the topic. We know how big an investment goes into monetizing visual content for our phones, pads and TVs, through the likes of Warner Media, Disney and Netflix. Now there’s a big push into monetizing our ears, driven by Apple and others on the… Read More

Verification Analytics: The New Paradigm with Cogita-PRO at DVCON 2026Cogita-PRO, developed by Vtool, introduces a transformative approach…Read More

Verification Analytics: The New Paradigm with Cogita-PRO at DVCON 2026Cogita-PRO, developed by Vtool, introduces a transformative approach…Read More Breker Hosts an Energetic Panel on Spec-Driven VerificationI was fortunate to be asked to moderate…Read More

Breker Hosts an Energetic Panel on Spec-Driven VerificationI was fortunate to be asked to moderate…Read MoreEven California Can’t Save Hydrogen

Fisita World Mobility Summit 2019 in Nagoya, Japan, brought together powerful perspectives on everything from vehicle architectures (Visteon), to open source software (Synopsys), mobility (METI), and connectivity (Bosch). The most enigmatic juxtaposition at the event, however, came in a panel discussion I moderated

Physical design team tackles challenging SoC

When describing the complexity of deep sub-micron systems on chip (SoCs), most engineers and their managers tend to refer to a combination of gate count, amount of embedded memory, and frequency of operation. If one’s task is to assess the complexity of the physical design effort for a given SoC, then there are numerous additional… Read More

Digital Retaliation of Iran – Top 6 Likely Cyber Attacks

The United States and allies’ national cyber response may soon be tested with the latest escalating conflict in the middle east. The U.S. conducted an airstrike that killed a revered Iranian general while in Iraq. This was in retaliation to a number of attacks against U.S. personnel and most recently the U.S. embassy in… Read More

The Tech Week that was January 6-10 2020

Happy New Year to everyone.. lets hope 2020 is a great year.. The indicators are all pointing in the right direction but it will not take much to derail it if external factors change. Here is my weekly summary of all the important news from the semiconductor industry around the world.

2020 is starting very differently from 2019 with… Read More

2020 The Year of Live In-Car Remote Assistance

After years of travel and computing remotely while on the road I have found that there are two magical experiences for the business traveler. One of those experiences is the hotline support I get from my preferred airline – United. The other is the live remote assistance I periodically receive from my company’s in-house IT department… Read More

China in 2020: Navigating the new policy landscape

This is the fourth of a five part series

Many companies saw 2019 as a year when more and more regulations piled on to them. CEOs who were the legal representative for their company in China got increasingly nervous as legal teams updated them on their personal responsibility under new regulations. Unfortunately for them, 2020 will… Read More

ASML EUV China Chip Equip Risk

- Is ASML first clandestine shot in US war on China chips?

- Will the action extend further to other chip equip cos?

- China chip cold conflict warming up?

It would appear from a Reuters report yesterday that a behind the scenes “cold war” between the US and China in the chip business has just been exposed and has the potential… Read More

CES 2020: Still no Flying Cars

CES 2020 is being held this week in Las Vegas with over 4,500 exhibiting companies and over 175,000 attendees. The show includes a broader industry than just electronics, which led to it being renamed CES (previously the Consumer Electronics Show) and the sponsoring organization changing its name from the Consumer Electronics… Read More

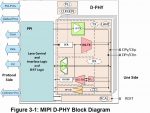

Mixel Makes Major Move on MIPI D-PHY v2.5

The MIPI Alliance has been running hard since 2003 to stay on top of the changes in the mobile industry. MIPI now has 250 member companies and 12 active working groups, all focused on creating standards for connecting the building blocks in mobile systems. MIPI based interfaces are now used in cars, drones, IoT devices, and of course… Read More

Captain America: Can Elon Musk Save America’s Chip Manufacturing Industry?