I had the good fortune to catch a live webinar recently that was quite compelling – Conversation with Dr. Walden Rhines: Predicting Semiconductor Business Trends After Moore’s Law! Dr. Rhines, known to most as Wally, doesn’t need much of an introduction. Any semiconductor or EDA professional knows who he is and what he’s accomplished.… Read More

Why TSMC is Known as the Trusted FoundryTaiwan Semiconductor Manufacturing Company (TSMC) is widely regarded…Read More

Why TSMC is Known as the Trusted FoundryTaiwan Semiconductor Manufacturing Company (TSMC) is widely regarded…Read More Journey Back to 1981: David Patterson Recounts the Birth of RISC and Its Legacy in RISC-VIn a warmly received keynote at the RISC-V…Read More

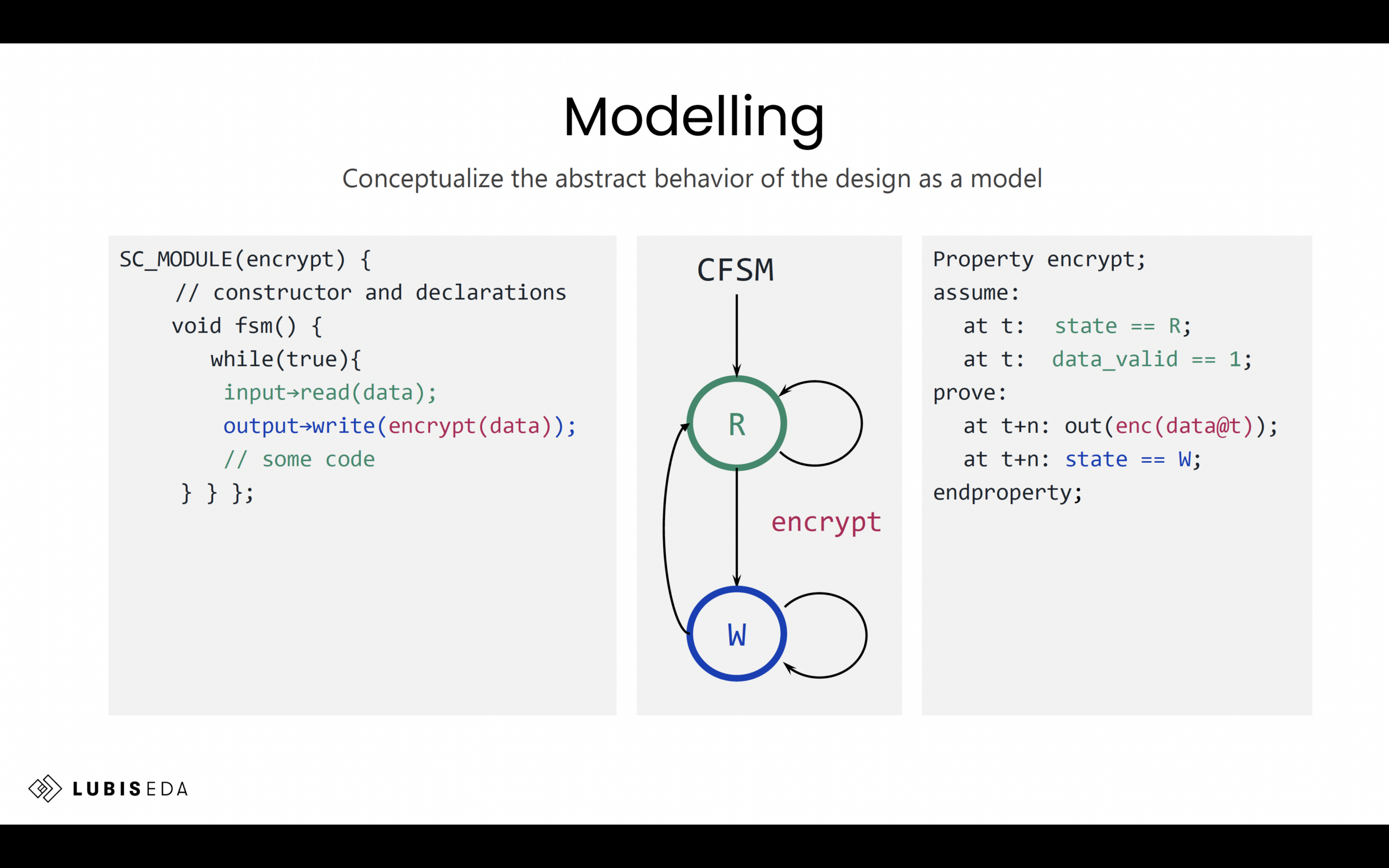

Journey Back to 1981: David Patterson Recounts the Birth of RISC and Its Legacy in RISC-VIn a warmly received keynote at the RISC-V…Read More Assertion-First Hardware Design and Formal Verification ServicesGenerative AI has transformed software development, enabling entire…Read More

Assertion-First Hardware Design and Formal Verification ServicesGenerative AI has transformed software development, enabling entire…Read More TSMC's Customized Technical Documentation Platform Enhances Customer ExperienceTaiwan Semiconductor Manufacturing Company, the world's leading dedicated…Read More

TSMC's Customized Technical Documentation Platform Enhances Customer ExperienceTaiwan Semiconductor Manufacturing Company, the world's leading dedicated…Read MoreWebinar: Design Methodologies for Next-Generation Heterogeneously Integrated 2.5/3D-IC Designs

I had the opportunity to preview the upcoming SemiWiki webinar titled: Design Methodologies for Next-Generation Heterogeneously Integrated 2.5/3D-IC Designs. John Park’s message, describing this powerful Cadence solution, really impressed me. That’s why I want to encourage you to register for it and join this SemiWiki … Read More

Why I’m Lowering Semiconductor Equipment Revenue Growth to -6.9% in 2020

Because of significant $4 billion in equipment pull-ins in Q4 from sales in Asia, I was reducing my semiconductor wafer front-end (WFE) equipment revenue growth from an earlier +5% to 0% in 2020. Now, based on CORVID-19, I am further reducing revenue growth to -6.9%.

Chart 1 also shows the cyclical nature of semiconductors and semiconductor… Read More

Learning to Live with the Gaps Between Design and Verification

Whenever I am asked to explain how chip design works by someone who is unfamiliar with the process, I struggle to explain the different steps in the flow. It also makes me aware of the discrete separations between each phase of activities. Of course, when you speak to a novice it is not even possible to get more than one layer down in the… Read More

A cautionary tale for the digital economy

COVID-19 underscores the importance of US-based production for strategic industries

The COVID-19 pandemic has drawn intense focus on the need to repatriate pharmaceutical manufacturing back to the United States. The increased awareness that a strategic adversary manufactures or controls up to 80% of the active pharmaceutical… Read More

Best Practices for IP Reuse

As someone who was heavily involved with rules for IP reuse for many years, I have a major sense of déja vu in writing again on the topic. But we (in SpyGlass) were primarily invested in atomic-level checks in RTL and gate-level designs. There’s a higher level of best practices in process we didn’t attempt to cover. ClioSoft just released… Read More

Lithography Resolution Limits: Paired Features

As any semiconductor process advances to the next generation or “node”, a sticky point is how to achieve the required higher resolution. As noted in another article [1], multipatterning (the required use of repeated patterning steps for a particular feature) has been practiced already for many years, and many have… Read More

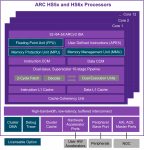

Synopsys is Changing the Game with Next Generation 64-Bit Embedded Processor IP

Synopsys issued a press release this morning that has some important news – Synopsys Introduces New 64-bit ARC Processor IP Delivering Up to 3x Performance Increase for High-End Embedded Applications. At first glance, one could assume this is just an announcement for some new additions to the popular ARC processor family. While… Read More

Webinar on Detecting Security Vulnerabilities in SoCs

As more security related capabilities are added in hardware it is changing the effort required to ensure that SoCs are not prone to attack. Hardware has the initial appeal of creating physical barriers to attack, yet it presents its own difficulties. For one thing, a flaw in a hardware security feature is much harder to fix in the … Read More

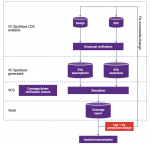

What’s New in CDC Analysis?

Synopsys just released a white paper, a backgrounder on CDC. You’ve read enough of what I’ve written on this topic that I don’t need to re-tread that path. However, this is tech so there’s always something new to talk about. This time I’ll cover a Synopsys survey update on numbers of clock domains in designs, also an update on ways to… Read More

Quantum Computing Technologies and Challenges