This topic is inspired by a presentation at last year’s DAC presented by Methodics, now part of Perforce. The issues raised by the original presentation are still quite relevant in the current business climate. IP leakage is something everyone should consider as part of their normal business operations. Your design IP really … Read More

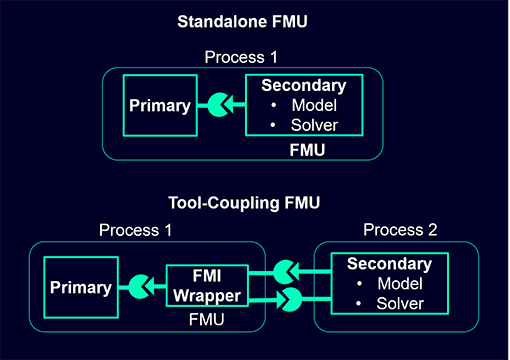

A Different Angle on Co-Simulation for SystemsCo-simulation, two or more simulations running concurrently in…Read More

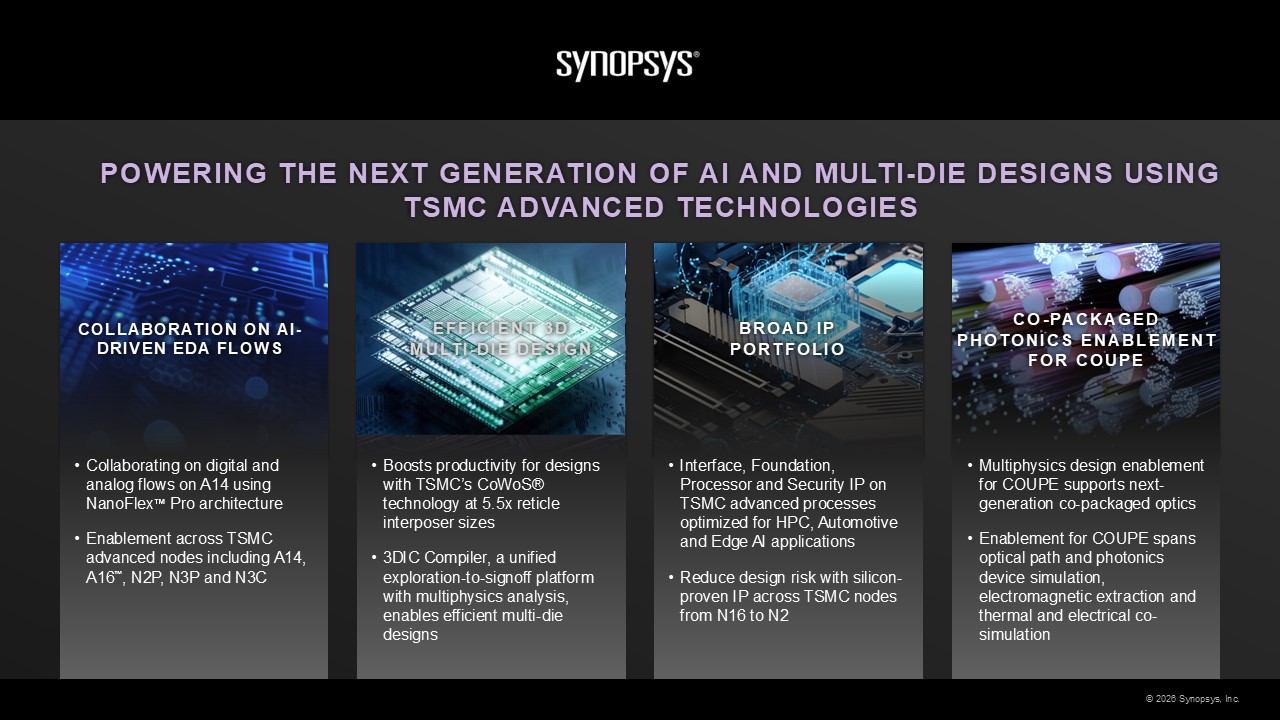

A Different Angle on Co-Simulation for SystemsCo-simulation, two or more simulations running concurrently in…Read More Synopsys and TSMC Deepen AI Design Alliance: What It MeansA recent announcement from Synopsys signals a meaningful…Read More

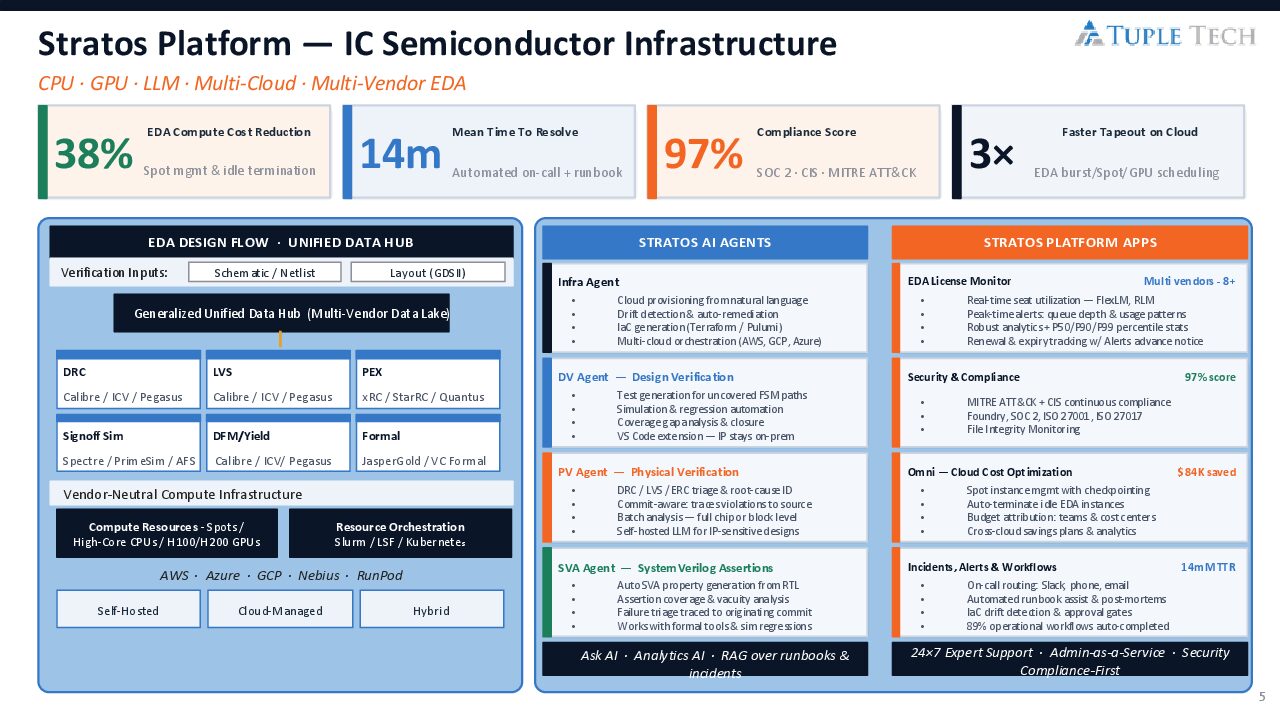

Synopsys and TSMC Deepen AI Design Alliance: What It MeansA recent announcement from Synopsys signals a meaningful…Read More Rethinking ECAD IT Infrastructure: From Fragmentation to an Engineering PlatformThe semiconductor industry is entering a new phase…Read More

Rethinking ECAD IT Infrastructure: From Fragmentation to an Engineering PlatformThe semiconductor industry is entering a new phase…Read MoreDeveloping Verification Flows for Silicon Photonics

Silicon photonics is getting a lot of interest because it can be used in many applications to improve bandwidth, reduce power and provide novel new functionality. It is especially interesting because it offers an ability to combine electronics and optical elements into the same die. Though it is fabricated with familiar silicon… Read More

Arm Announces Neoverse Update, Immediately Following V9

Among marketing principles, “Stay Visible’ must rank as one of the highest. Meaning that if you don’t have something new to announce on a regular basis, you disappear. Most important, among the people you hope to influence, you cease to exist. As true for small ventures as large, though small ventures struggle to understand or prioritize… Read More

Formal Verification Approach Continues to Grow

After a few decades of watching formal verification techniques being applied to SoC designs, it certainly continues to be a growth market for EDA vendors. In the first decades from 1970-1990 the earliest forms of formal tools emerged at technical conferences, typically written by University students earning their Ph.D.s, … Read More

3rd Party Semiconductor Intellectual Property Market Update

The 3rd Party Semiconductor Intellectual Property (IP) market has seen great innovation in the products it offers to System-on-a-Chip (SoC) designers over the last ten years. If any market segment in the semiconductor industry typifies the intense evolutionary pressures that the entire electronics market has undergone, … Read More

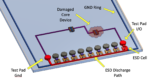

Magwel Adds Core Device Checking for ESD Verification

In the past ESD sign-off has been accomplished by a combination of techniques. Often ESD experts are asked to look at a design and assess its ESD robustness based on experience gained from prior chips. Alternatively, designers are told to work with a set of rules given to them, again based on previous experience about what usually… Read More

Cadence Extends Tensilica Vision, AI Product Line

Vision pipelines, from image signal processing (ISP) through AI processing and fancy effects (super-resolution, Bokeh and others) has become fundamental to almost every aspect of the modern world. In automotive safety, robotics, drones, mobile applications and AR/VR, what we now consider essential we couldn’t do without… Read More

Webinar: System Level Modeling and Analysis of Processors and SoC Designs

Engineers love to optimize their designs, but that implies that there are models and stimulus to automate the process. Process engineers have TCAD tools, circuit designers have SPICE for circuit simulation, logic designers have gate-level simulators, RTL designers use logic simulation, but what is there for the system architects… Read More

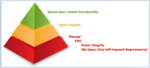

Samtec Keynote – Power Integrity is the New Black Magic

The Signal Integrity Journal recently held a half day Electronic Systems SI/PI Forum that included presentations from industry leaders covering key design topics for signal integrity and power integrity engineers. The event was sponsored by Cadence. The keynote for the event was presented by Istvan Novak, principal signal… Read More

Mars Perseverance Rover Features First Zoom Lens in Deep Space

On July 30, 2020, NASA launched the Mars 2020 Perseverance rover, which is scheduled to land today. Perseverance has been deployed to Mars with a new mission: to search for evidence of past life and collect samples that will eventually be brought back to Earth by future missions.

Siemens U2U 3D IC Design and Verification Panel