We all know signal integrity and power integrity are becoming more important for advanced design. Like package engineering, the obscure and highly technical art of SI/PI optimization has taken center stage in the design process. And the folks who command expertise in these areas have become the rock stars of the design team. I … Read More

Exploring the Hidden Complexity of Modern Power Electronics Design – A Siemens White PaperReview the specifications of any state-of-the-art microcontroller and…Read More

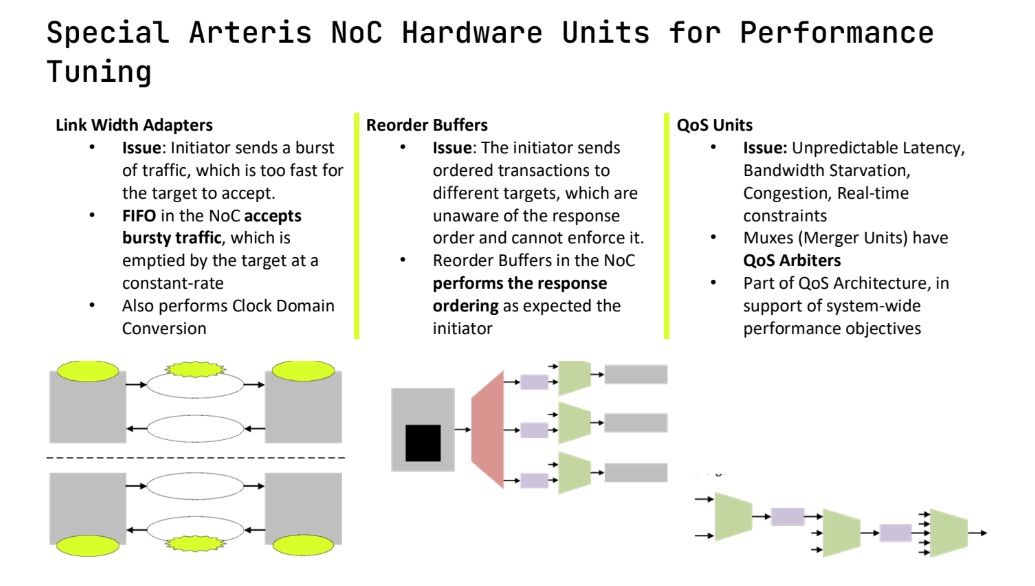

Exploring the Hidden Complexity of Modern Power Electronics Design – A Siemens White PaperReview the specifications of any state-of-the-art microcontroller and…Read More Renesas Scalable Automotive SoC Design Using Arteris NoCThe increasing complexity of advanced driver assistance systems…Read More

Renesas Scalable Automotive SoC Design Using Arteris NoCThe increasing complexity of advanced driver assistance systems…Read More Calibrating Quantum Computing Activity in Financial ServicesI was invited to listen in on an…Read More

Calibrating Quantum Computing Activity in Financial ServicesI was invited to listen in on an…Read More NoC Matters: Designing the Backbone of Next-Gen AI SoCsModern SoC design for artificial intelligence workloads has…Read More

NoC Matters: Designing the Backbone of Next-Gen AI SoCsModern SoC design for artificial intelligence workloads has…Read MoreAssembly Automation. Repair or Replace?

It is difficult to imagine an SoC development team not using some form of automation to assemble their SoCs; the sheer complexity of the assembly task for modern designs is already far beyond hand-crafted top-level RTLs. An increasing number of groups have already opted for solutions based on the IP-XACT integration standard.… Read More

OnStar: Getting Connectivity Wrong

One of my pet beefs with the car industry is that car makers, on the whole, have failed to agree among themselves as to what basic vehicle connectivity ought to consist of. From car maker to car maker prices vary, bundles vary, free periods of service access vary and the variations get worse between model years as offers change and … Read More

LRCX weak miss results and guide Supply chain worse than expected and longer to fix

-Lam missed on both top & bottom line due to supply chain

-Previous guide was “overly optimistic” about fixing issues

-Demand is great but doesn’t matter if you can’t serve it

-We remain concerned about ability to fix issues in near term.

A miss on numbers- supply issues will persist

Lam reported Revenues… Read More

Podcast EP73: Adventures in Supercomputing with Luminous Computing and Andes Technology

Dan is joined by Dr. Dave Baker, VP digital design at Luminous Computing and John Min, director of field applications at Andes Technology. Dave and John explore with Dan their collaboration to build high-performance supercomputers.

The views, thoughts, and opinions expressed in these podcasts belong solely to the speaker, … Read More

Chip Enabler and Bottleneck ASML

-ASML reported an “in line” Q1- Orders remain super strong

-Ongoing supply chain issues will limit growth and upside

-ASML targets 2025 for supply fixes- We are not so sure

-Intel, TSMC, Samsung won’t be able to build all fabs they plan

ASML has “In linesh” Q1, orders still off the charts

ASML reported… Read More

Truechip’s DisplayPort 2.0 Verification IP (VIP) Solution

Integrating IP to build SoCs has been consistently on the rise. Growth in complexity and meeting time to market pressures are some primary drivers behind this phenomenon. Consequentially, the IP market segment has also been enjoying tremendous growth. While this is great news for chip design schedules, it does highlight the … Read More

The ASIC Business is Surging!

Application Specific Integrated Circuits were the foundation of the semiconductor industry up until the IDMs came to power in the 1980s and 90s. Computer companies all had their own fabs, I worked in one, until start up companies like SUN Microsystems started using off the shelf chips from Motorola. SUN moved to the fabless model… Read More

Podcast EP72: Analog AI/ML with Aspinity

Dan is joined by Tom Doyle, CEO of Aspinity. Dan explores the benefits of Aspinity’s analog signal processing technology with Tom. The ultra-low power analog computing capability delivered by Aspinity has significant implications for the design and deployment of AI/ML systems.

The views, thoughts, and opinions… Read More

Visual Debug for Formal Verification

Success with Open-Source Formal Verification

The dream of 100% confidence is compelling for silicon engineers. We all want that big red button to push that magically finds all of our bugs for us. Verification, after all, accounts for roughly two-thirds of logic design effort. Without that button, we have to create reference models,… Read More

Disaggregating LLM Inference: Inside the SambaNova Intel Heterogeneous Compute Blueprint