After many years of hesitancy to jump with both feet in, semiconductor companies are seriously considering implementing cloud strategies and making required investments. Their concern though is, how much investment is it going to take? Some of the block-and-tackle challenges they face in implementing a cloud strategy are … Read More

Synopsys Advances Hardware Assisted Verification for the AI EraAt the 2026 Synopsys Converge Event, Synopsys announced…Read More

Synopsys Advances Hardware Assisted Verification for the AI EraAt the 2026 Synopsys Converge Event, Synopsys announced…Read More Chemical Origins of Environmental Modifications to MOR Lithographic ChemistryIn the pursuit of advanced extreme ultraviolet (EUV)…Read More

Chemical Origins of Environmental Modifications to MOR Lithographic ChemistryIn the pursuit of advanced extreme ultraviolet (EUV)…Read More Post-Silicon Validating an MMU. Innovation in VerificationSome post-silicon bugs are unavoidable, but we’re getting…Read More

Post-Silicon Validating an MMU. Innovation in VerificationSome post-silicon bugs are unavoidable, but we’re getting…Read More Securing UALink in AI clusters with UALinkSec-compliant IPA classic networking problem is securing connections with…Read More

Securing UALink in AI clusters with UALinkSec-compliant IPA classic networking problem is securing connections with…Read More0.55 High-NA Lithography Update

At the recent SPIE Advanced Lithography + Patterning Conference, Mark Phillips from Intel gave an insightful update on the status of the introduction of the 0.55 high numerical aperture extreme ultraviolet lithography technology. Mark went so far as to assert that the development progress toward high-NA EUV would support … Read More

Using EM/IR Analysis for Efinix FPGAs

I’ve been following the EM/IR (Electro-Migration, IR is current and resistance) analysis market for many years now, and recently attended a presentation from Steven Chin, Sr. Director IC Engineering of Efinix, at the User2User event organized by Siemens EDA. The Tuesday presentation was in the morning at the Marriott… Read More

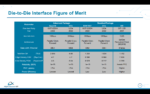

Die-to-Die IP enabling the path to the future of Chiplets Ecosystem

The topic of chiplets is getting a lot of attention these days. The chiplet movement has picked up more momentum since Moore’s law started slowing down as process technology approached 5nm. With the development cost of a monolithic SoC crossing the $500M and wafer yields of large die-based chips dropping steeply, the decision … Read More

Connecting Everything, Everywhere, All at Once

The automotive industry is rapidly coming to the realization that connecting cars is about so much more than simply adding a modem, an antenna, and a bit of software. Connecting cars and connecting car owners with an attractive connectivity value proposition may be two of the most difficult things the industry has ever attempted.… Read More

Podcast EP82: The Critical Need for Reliability in Future Products

Dan is joined by Charlie Slayman, technical leader at Cisco Systems working on reliability physics and risk assessment of advanced semiconductor technology. He is also the general chair of the International Reliability Physics Symposium, or IRPS which is the focus of the discussion.

Dan explores the rapidly growing application… Read More

The New Normal for Semiconductor Manufacturing

One of the recent live events I attended was the 2022 GSA Silicon Leadership Summit on May 12th at the Santa Clara Convention Center (my favorite location). This was the first GSA live event in two years so it was a must attend gathering. This event targets semiconductor ecosystem executives (200+ people attended) so there were many… Read More

Methods for Current Density and Point-to-point Resistance Calculations

IC reliability is an issue that circuit design engineers and reliability engineers are concerned about, because physical effects like high Current Density (CD) in interconnect layers, or high point-to-point (P2P) resistance on device interconnect can impact reliability, timing or Electrostatic Discharge (ESD) robustness.… Read More

Very Short Reach (VSR) Connectivity for Optical Modules

Bandwidth, latency, power and reach are always the key points of focus when it comes to connectivity. As the demand for more data and higher bandwidth connectivity continue, power management is gaining a lot of attention. There is renewed interest in pursuing silicon photonics to address many of these challenges. There are many… Read More

[WEBINAR] Secure your devices with PUF plus hardware root-of-trust

It’s a hostile world we live in, and cybersecurity of connected devices is a big concern. Attacks are rising rapidly, and vulnerabilities get exploited immediately. Supply chains are complex. Regulations are proliferating. Secrets don’t stay secrets for long – in fact, the only secret in a system with open-source algorithms… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center