While Truechip has established itself as a global provider of verification IP (VIP) solutions, they are always on the lookout for strategic IP needs from their customer base. Over the last several years, a solid market for Network-on-Chip (NoC) IP has grown, driven by the need to rapidly move data across a chip. Concurrently, the… Read More

Arteris Highlights a Path to Scalable Multi-Die Systems at the Chiplet SummitAt the recent Chiplet Summit, presentations, discussions and…Read More

Arteris Highlights a Path to Scalable Multi-Die Systems at the Chiplet SummitAt the recent Chiplet Summit, presentations, discussions and…Read More Captain America: Can Elon Musk Save America's Chip Manufacturing Industry?Intel has posted three consecutive years of falling…Read More

Captain America: Can Elon Musk Save America's Chip Manufacturing Industry?Intel has posted three consecutive years of falling…Read More WEBINAR: Reclaiming Clock Margin at 3nm and BelowAt 3nm and below, clock networks have quietly…Read More

WEBINAR: Reclaiming Clock Margin at 3nm and BelowAt 3nm and below, clock networks have quietly…Read More WEBINAR: HBM4E Advances Bandwidth Performance for AI TrainingThe rapid proliferation of LLMs and other AI…Read More

WEBINAR: HBM4E Advances Bandwidth Performance for AI TrainingThe rapid proliferation of LLMs and other AI…Read More Siemens Wins Best in Show Award at Chiplet Summit and Targets Broad 3D IC Design EnablementThe recent Chiplet Summit in Santa Clara was…Read More

Siemens Wins Best in Show Award at Chiplet Summit and Targets Broad 3D IC Design EnablementThe recent Chiplet Summit in Santa Clara was…Read MoreYour Symmetric Layouts show Mismatches in SPICE Simulations. What’s going on?

This Diakopto paper discusses for the first time, a new effect – a false electrical mismatch in post-layout simulations for perfectly symmetric nets. This effect is caused by the difference in distributions of parasitic coupling capacitors over the nodes of parasitic resistor networks, even for symmetric nets. This, in turn,… Read More

Musk: The Post-Truth Messiah

The hand-wringing over Elon Musk’s takeover of Twitter began in earnest, Friday, as General Motors announced it would suspend advertising on the platform. Ford Motor Company, too, said it would take a step back.

The news of Musk’s completion of his Twitter acquisition completely eclipsed Mobileye’s hugely successful… Read More

Podcast EP119: The Latest Innovations at Agile Analog with Barry Paterson

Dan is joined by Barry Paterson, CEO of Agile Analog. Barry has held senior leadership, engineering and product management roles at Wolfson Microelectronics and Dialog Semiconductor. He has been involved in the development of custom mixed-signal silicon solutions for many of the leading mobile and consumer electronics … Read More

Pushing Acceleration to the Edge

As more AI applications turn to edge computing to reduce latencies, the need for more computational performance at the edge continues to increase. However, commodity compute engines don’t have enough compute power or are too power-hungry to meet the needs of edge systems. Thus, when designing AI accelerators for the edge, Joe… Read More

Elevating Production Testing with proteanTecs and Advantest’s ACS Edge™ Platforms

SemiWiki recently posted a blog on “Deep Data Analytics for Accelerating SoC Product Development.” That blog focused on proteanTecs’ AI-enabled chip analytics platform that helps accelerate SoC product development. The blog provided insight into proteanTecs’ approach and shared quantifiable business-impact metrics … Read More

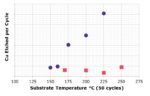

Step into the Future with New Area-Selective Processing Solutions for FSAV

Area selective processing (ASP) is assuming ever greater importance in semiconductor fabrication. ASP involves deposition and removal of materials at the molecular level¾10 nm or less. Key applications of ASP include self-aligned contacts and fully self-aligned vias (FSAVs), scaling boosters that are essential to continue… Read More

Podcast EP118: An Assessment of the Worldwide Semiconductor Ecosystem with Sagar Pushpala

Dan is joined by Sagar Pushpala, a seasoned semiconductor professional with more than 35 years of experience with IDMs, fabless and related semiconductor entities. He is actively involved with nearly a dozen companies in the US, Singapore and India in advisory/board, consulting and investment roles.

Dan explores the dynamics… Read More

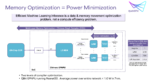

Slashing Power in Wearables. The Next Step

In wearables and hearables, low power is king. Earbuds for example still only manage a half-day active use before we need to recharge. Half a day falls short of truly convenient for most of us – a full day would be much better, allowing for overnight recharge. Physics limits battery sizes so system designers must look to SoC architectures… Read More

Quadric’s Chimera GPNPU IP Blends NPU and DSP to Create a New Category of Hybrid SoC Processor

Performance, Power and Area (PPA) are the commonly touted metrics in the semiconductor industry placing PPA among the most widely used acronyms relating to chip development. And rightly so as these three metrics greatly impact all electronic products that are developed. The degree of impact depends of course on the specific … Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era