The pursuit of ever smaller DRAM cell sizes is still active and ongoing. DRAM cell size is projected to approach 0.0013 um2 for the D12 node. Patterning challenges are significant whether considering the use of DUV or EUV lithography. In particular, ASML reported that when center-to-center values reached 40 nm, single patterning… Read More

Synopsys Advances Hardware Assisted Verification for the AI EraAt the 2026 Synopsys Converge Event, Synopsys announced…Read More

Synopsys Advances Hardware Assisted Verification for the AI EraAt the 2026 Synopsys Converge Event, Synopsys announced…Read More Chemical Origins of Environmental Modifications to MOR Lithographic ChemistryIn the pursuit of advanced extreme ultraviolet (EUV)…Read More

Chemical Origins of Environmental Modifications to MOR Lithographic ChemistryIn the pursuit of advanced extreme ultraviolet (EUV)…Read More Post-Silicon Validating an MMU. Innovation in VerificationSome post-silicon bugs are unavoidable, but we’re getting…Read More

Post-Silicon Validating an MMU. Innovation in VerificationSome post-silicon bugs are unavoidable, but we’re getting…Read More Securing UALink in AI clusters with UALinkSec-compliant IPA classic networking problem is securing connections with…Read More

Securing UALink in AI clusters with UALinkSec-compliant IPA classic networking problem is securing connections with…Read MoreAlphawave IP is now Alphawave Semi for a very good reason!

The semiconductor ecosystem has been full of interesting twists of late and Alphawave has been a company to watch since the very beginning. Alphawave came out of stealth mode in early 2019 as the world’s first IP company focused on multi-standard connectivity (SerDes) IP solutions. The importance of SerDes had been understated… Read More

Where there’s Smoke there’s Fire: UCTT ICHR LRCX AMAT KLAC Memory

-UCTT & ICHR both pre announce ugly QTR & blame memory

-LRCX is the memory “poster child” & most impacted

-This is on top of China & Economic issues & memory specific

-Clearing out inventory is a sign of expected slow recovery

UCTT & ICHR pre-announce ugly quarters

Both UCTT & ICHR that … Read More

Who will Win in the Chiplet War?

The first Chiplet specific conference is coming up which is a milestone in itself. As we know the only thing new about chiplets is the name but when there is a dedicated conference to such a specific thing you know it has officially “arrived”. There is even a cool new tagline: Chiplets make huge chips happen!

“The First Annual Chiplet… Read More

Podcast EP137: The International Impact of Accellera’s Work

Dan is joined by Lu Dai who is currently a Senior Director of Technical Standards at Qualcomm. Previously he was Senior Director of Engineering, leading Qualcomm’s SoC design verification team and front-end methodologies and initiatives. Lu is Chair of Accellera Systems Initiative and serves on the Board of Directors at RISC-V… Read More

CEO Interview: Matt Genovese of Planorama Design

Matt Genovese is the founder and CEO of Planorama Design, bringing over 25 years of career experience in high-tech, spanning semiconductors, hardware, IoT, IT, and software product development. He has a strong track record of planning, launching, and shipping products that work. Matt’s company, Planorama Design, is a software… Read More

To EV or NOT to EV?

It’s anybody’s guess when it comes to future demand for EVs. KPMG is the latest to put a perspective out on the subject – drastically slashing timelines for EV adoption based on a survey of senior industry executives. KPMG says the surveyed executives reported a median expectation for EV adoption by 2030 to 35% of sales from 65% … Read More

Podcast EP136: Semiconductor Industry Update with Malcolm Penn

Dan is joined by Malcolm Penn, CEO of Future Horizons. Malcolm is a contributor to SemiWiki and a frequent podcast guest.

Dan and Malcolm discuss what happened in the semi industry last year and what 2023 and 2024 will look like and why. The discussion is a preview to Malcolm’s upcoming Industry Update Webinar on January … Read More

CES is Back, but is the Market?

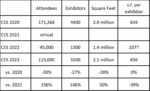

CES 2023, the annual consumer technology show, was held last week in Las Vegas, Nevada. Over 115,000 people attended and over 3200 companies exhibited. As shown below, attendance and exhibitors were up about 2 ½ times the pandemic limited CES 2022. However, attendance was down one-third and exhibitors were down 27% from CES 2020.… Read More

CES 2023 and all things cycling

It’s January so time for me to review what I’ve found at CES this year that relates to cycling. Unlike last year when there were many last-minute cancellations from exhibitors, in 2023 it’s in-person and bigger than ever. The electrification of bikes continues, and many of these electronic devices are cloud… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center