High volume manufacturing is a 24/7 business with 12 hour shifts. You don’t always get to pick the shifts you want and you must cover for others when they can’t. It’s a challenging career and not for the faint of heart like myself.

In the 1980s and 1990s I spent time in Japan working with some of the top Japanese semiconductor manufacturers.… Read More

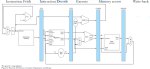

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center