MZ Technologies is a unique company that enables multi-die design by providing critical planning and analysis tools that sit above the traditional EDA design flow. Chip and package design tools are good at what they do. Given a set of constraints, they will deliver a good result. The question is, what is the right set of constraints? … Read More

CEO Interview with Nagesh Gupta of llmda.aiNagesh has built a career spanning multiple aspects…Read More

CEO Interview with Nagesh Gupta of llmda.aiNagesh has built a career spanning multiple aspects…Read More The "New Shift-Left": Why FPGA Prototyping is the Ultimate RISC-V IP SandboxIn the EDA world, "Shift-Left" has traditionally been…Read More

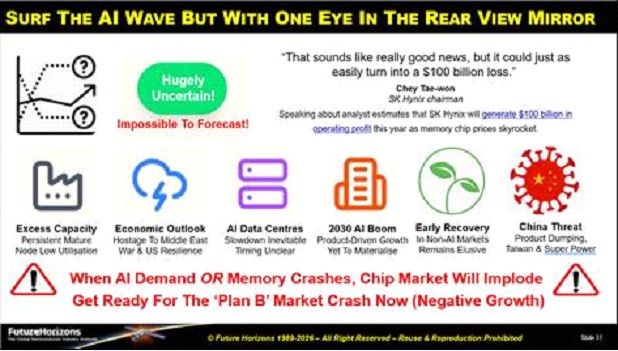

The "New Shift-Left": Why FPGA Prototyping is the Ultimate RISC-V IP SandboxIn the EDA world, "Shift-Left" has traditionally been…Read More The Semiconductor Growth Numbers are Insane but the Real World Doesn’t Tally!May’s WSTS Report saw March’s total monthly semiconductor…Read More

The Semiconductor Growth Numbers are Insane but the Real World Doesn’t Tally!May’s WSTS Report saw March’s total monthly semiconductor…Read More SiFive’s P570 Gen 3 Pushes RISC-V Further Into the AI EraWith the launch of its new P570 Gen…Read More

SiFive’s P570 Gen 3 Pushes RISC-V Further Into the AI EraWith the launch of its new P570 Gen…Read More CEO Interview with Dr. Jekaterina Viktorova of SyentaDr. Jekaterina (Jeka) Viktorova is the CEO and…Read More

CEO Interview with Dr. Jekaterina Viktorova of SyentaDr. Jekaterina (Jeka) Viktorova is the CEO and…Read MorePodcast EP214: The Broad Impact of proteanTecs with Noam Brousard

Dan is joined by Noam Brousard, who has over 20 years of diverse technology experience, spanning systems engineering, software development and hardware design. He currently serves as the vice president of Solutions Engineering at proteanTecs, where he helps customers implement on-chip monitoring solutions to address their… Read More

LIVE WEBINAR: RISC-V Instruction Set Architecture: Enhancing Computing Power

In the dynamic landscape of chip design, two trends stand out as game-changers: the rise of the RISC-V instruction set architecture (ISA) and the advent of Software Defined products. Today, we delve into why these trends are not just shaping the industry but propelling companies like Andes and Menta to the forefront of innovation.… Read More

Synopsys SNUG Silicon Valley Conference 2024: Powering Innovation in the Era of Pervasive Intelligence

After the leadership transition at the top, Synopsys had just a little more than two months before the company’s flagship event, the Synopsys User Group (SNUG) conference. The Synopsys user community and entire ecosystem were waiting to hear new CEO Sassine Ghazi’s keynote to learn where the company is going and its strategic … Read More

Ultra-low-power MIPI use case for streaming sensors

MIPI built its reputation on the efficient streaming of data from camera sensors in mobile devices. It combines high-speed transfers with balanced power consumption, helping extend battery life while providing the responsiveness users expect. However, high speed is not the only mode of operation for a MIPI interface – specifications… Read More

Arm Automotive Update Stresses Prototyping for Software Development

If you were at all uncertain about auto OEM development priorities, the answer is becoming clear: to accelerate/shift left automotive software development and debug. At 100M lines of code and accelerating, this task is overshadowing all others. A recent Arm update from Dipti Vachani (SVP and GM for the Automotive Line of Business)… Read More

2024 Outlook with Srinivasa Kakumanu of MosChip

MosChip is a publicly traded company founded in the year 1999, they offer semiconductor design services, turnkey ASIC, software services, and end-to-end product engineering solutions. The company headquartered in Hyderabad, India, with five design centers and over 1300 engineers located in Silicon Valley (USA), Hyderabad,… Read More

Fault Simulation for AI Safety. Innovation in Verification

More automotive content 😀

In modern cars, safety is governed as much by AI-based functions as by traditional logic and software. How can these functions be fault-graded for FMEDA analysis? Paul Cunningham (GM, Verification at Cadence), Raúl Camposano (Silicon Catalyst, entrepreneur, former Synopsys CTO and now Silvaco CTO)… Read More

A Modeling, Simulation, Exploration and Collaborative Platform to Develop Electronics and SoCs

During the GOMACTech conference held in South Carolina last week I had a Zoom call with Deepak Shankar, Founder and VP Technology at Mirabilis Design Inc. to ask questions and view a live demo of VisualSim – a modeling, simulation, exploration and collaborative platform to develop electronics and SoCs. What makes VisualSim so … Read More

Weebit Nano Brings ReRAM Benefits to the Automotive Market

Non-volatile memory (NVM) is a critical building block for most electronic systems. The most popular NVM technology has traditionally been flash. As a discrete part, the technology can be delivered in various form factors. For embedded applications flash presents scaling challenges, however. A new NVM technology developed… Read More

From the Selfie to Samantha: The Next Trillion-Dollar Behavior