At CadenceLIVE 2024 Anirudh Devgan (President and CEO of Cadence) hosted two fireside chats, one with Jensen Huang (President and CEO of NVIDIA) and one with Cristiano Amon (President and CEO of Qualcomm). As you would expect both discussions were engaging and enlightening. What follows are my takeaways from those chats.

Sensors Converge: Where Intelligence Meets the EdgeThe Sensors Converge Conference is one of the…Read More

Sensors Converge: Where Intelligence Meets the EdgeThe Sensors Converge Conference is one of the…Read More Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data CenterAt the TERAFAB launch event in Austin on…Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data CenterAt the TERAFAB launch event in Austin on…Read More Synopsys Advances Hardware Assisted Verification for the AI EraAt the 2026 Synopsys Converge Event, Synopsys announced…Read More

Synopsys Advances Hardware Assisted Verification for the AI EraAt the 2026 Synopsys Converge Event, Synopsys announced…Read More Chemical Origins of Environmental Modifications to MOR Lithographic ChemistryIn the pursuit of advanced extreme ultraviolet (EUV)…Read More

Chemical Origins of Environmental Modifications to MOR Lithographic ChemistryIn the pursuit of advanced extreme ultraviolet (EUV)…Read MoreARC-V portfolio plus mature software IP targets three tiers

Synopsys is bridging its long-running ARC® processor IP strategy into a RISC-V architecture – Bernard Murphy introduced the news here on SemiWiki last November. We’re getting new insight from Synopsys on its ARC-V™ portfolio and how they see RISC-V IP plus their mature software development toolchain IP fitting customer needs… Read More

Siemens EDA Makes 3D IC Design More Accessible with Early Package Assembly Verification

2.5D and 3D ICs present special challenges since these designs contain multiple chiplets of different materials integrated in all three dimensions. This complexity demands full assembly verification of the entire stack, considering all the subtle electrical and physical interactions of the complete system. Identifying… Read More

Podcast EP222: The Importance of Managing and Preserving Ultrapure Water in Semiconductor Fabs with Jim Cannon

Dan is joined by Jim Cannon, Head of OEM and Markets at Mettler-Toledo Thornton. Jim has over 35 years of experience managing, designing, and developing ultrapure water treatment and technology. Jim is currently involved in the standards and regulatory organizations including the Facilities and Liquid Chemicals Committee,… Read More

Webinar: Fine-grained Memory Protection to Prevent RISC-V Cyber Attacks

Most organizations are aware of cybercrime attempts such as phishing, installing malware from dodgy websites or ransomware attacks and undertake countermeasures. However, relatively little attention has been given to memory safety vulnerabilities such as buffer overflows or over-reads. For decades, the industry has created… Read More

CEO Interview: Dr. Nasib Naser of ORION VLSI Technologies.

Dr. Nasib Naser brings over 35 years of experience in the field. His expertise spans the entire VLSI cycle from conception to chip design, with a strong focus on verification methodologies. For his 17 years at Synopsys, Dr. Naser have held senior management positions, leading North American Verification IP, managing Central … Read More

Webinar: Samtec and Achronix Expand AI in the Data Center

The performance demands of data centers continue to grow, driven to large degree by the ubiquitous use of complex AI algorithms. On April 25, Embedded Computing Design held an informative webinar on this topic. Two experts looked at the problem from the standpoint of processor architecture and communication strategies, which… Read More

Don’t Settle for Less Than Optimal – Get the Perfect Inductor Every Time

The meaning of the word “Veloce” is “blazing fast”. It is the inspiration behind the name of the Ansys VeloceRF electromagnetic (EM) passive device synthesis platform that has been a favorite among RF and high-speed integrated circuit (IC) designers for more than 15 years. VeloceRF is a name that designers automatically connect… Read More

Synopsys is Paving the Way for Success with 112G SerDes and Beyond

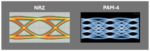

Data communication speeds continue to grow. New encoding schemes, such as PAM-4 are helping achieve faster throughput. Compared to the traditional NRZ scheme, PAM4 can send twice the signal by using four levels vs. the two used in NRZ. The diagram at the top of this post shows the how data density is increased. With progress comes… Read More

Oops, we did it again! Memory Companies Investment Strategy

We are in the semiconductor market phase where everybody disagrees on what is going on. The market is up; the market is down. Mobile phones are up…. oh no, now they are down. The PC market is up—oh no, we need to wait until we can get an AI PC. The inflation is high—the consumer is not buying.

For us in the industry, the 13-week financial … Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center