What I’m really describing here is an over-simplified backend flow for physical design of low power ICs with multiple voltage domains. If you haven’t ventured into this territory yet, this will hopefully give you some food for thought. Here are the basic steps:… Read More

UX in Agentic Systems. Innovation in VerificationA switch this month to principles behind building…Read More

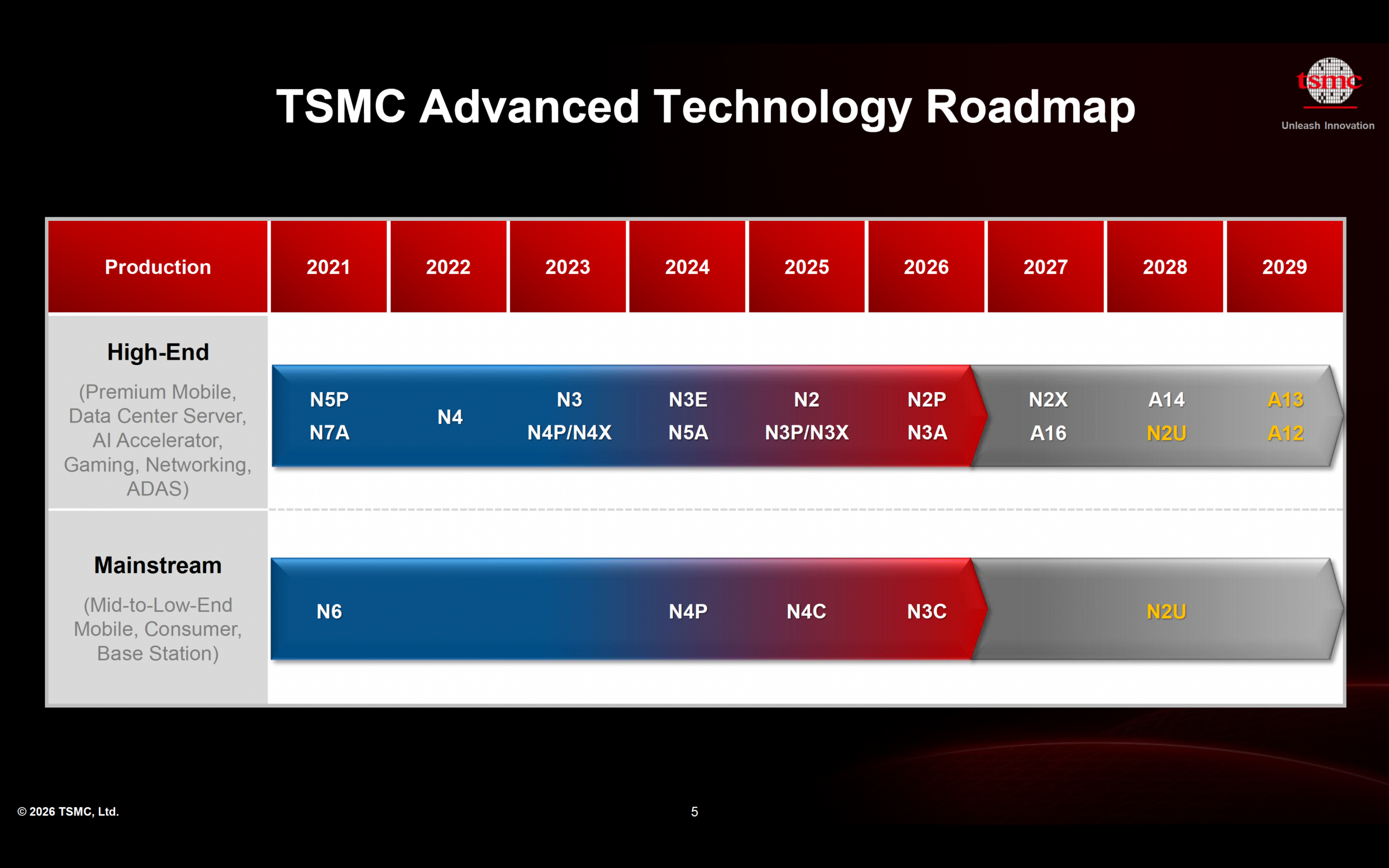

UX in Agentic Systems. Innovation in VerificationA switch this month to principles behind building…Read More The Shift to System-Level AI Drives Next-Generation SiliconAt its 2026 Technology Symposium, TSMC delivered a…Read More

The Shift to System-Level AI Drives Next-Generation SiliconAt its 2026 Technology Symposium, TSMC delivered a…Read More All in One Bluetooth Audio: A Complete Solution on a TSMC 12nm Single DieThe rapid evolution of wireless audio has placed…Read More

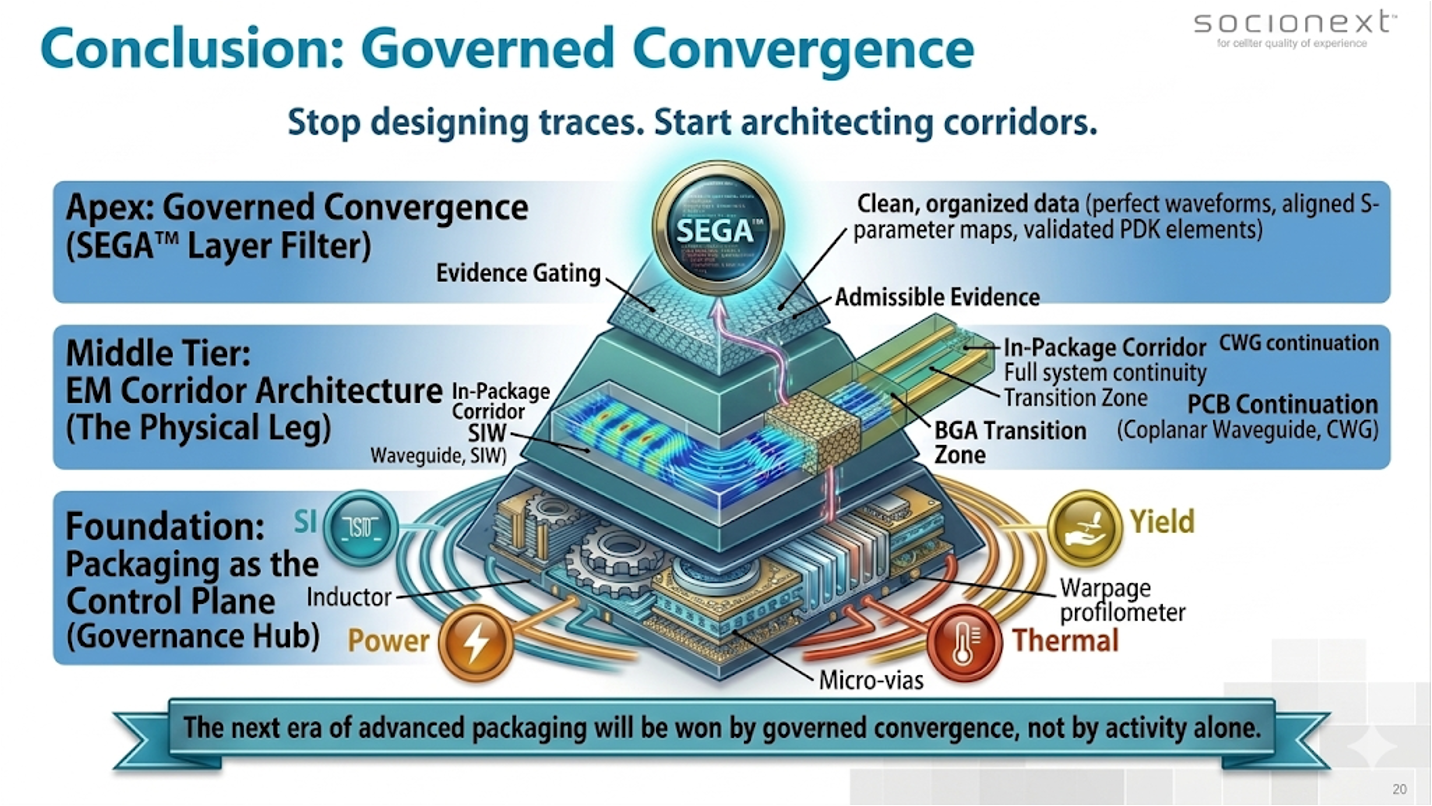

All in One Bluetooth Audio: A Complete Solution on a TSMC 12nm Single DieThe rapid evolution of wireless audio has placed…Read More Closing the Reality Gap: A New Architecture for 1.8-Tb/s Chiplet GovernanceBy Dr. Moh Kolbehdari Dr. Moh Kolbehdari is…Read More

Closing the Reality Gap: A New Architecture for 1.8-Tb/s Chiplet GovernanceBy Dr. Moh Kolbehdari Dr. Moh Kolbehdari is…Read More SemiWiki Q&A with Julie Rogers, Executive Director, ESD AllianceThe Electronic System Design Alliance (ESD Alliance), a SEMI…Read More

SemiWiki Q&A with Julie Rogers, Executive Director, ESD AllianceThe Electronic System Design Alliance (ESD Alliance), a SEMI…Read MoreClocks Will Be Clocks

Clock designers are an enigma. Clock designers in general are die hard Star Wars fans, own vintage Porsches that leak oil by the gallon, usually have lava lamps in their offices/cubicles, wear fancy leather jackets in the peak of summer, and have like-minded clock designers as best lunch buddies. … Read More

Why Only MV When You Can MC, MM & MV?

Resistance is futile. I recently caved and switched to an iPhone after having been a loyal Google phone user for more than year. Apart from the coolness factor, my main motivation was corporate mail support that was absent in Gphone, plus the fact that I got the iPhone for free when my wife upgraded hers. The difference is day and night… Read More

How to Multi-Voltage IC Design in 10 Easy Steps

What I’m really describing here is an over-simplified backend flow for physical design of low power ICs with multiple voltage domains. If you haven’t ventured into this territory yet, this will hopefully give you some food for thought. Here are the basic steps:… Read More

So, Why Not Just Write Better Rules?

In my submission about TSMC making some DFM analysis steps mandatory at 45nm (see “TSMC’s DFM Announcement”), I ended with a question about why the foundries can’t just write better design rules (and rule decks) to make sure all designs yield well. Here’s my take on this complicated question.… Read More

TSMC’s DFM Announcement

If you are a TSMC customer, no doubt you have heard TSMC is requiring lithography and planarity analysis for all 45nm designs. Their website says customers can either run it themselves, or contract TSMC services to do it. The most cost-effective way would be for the customers to run it themselves, but some might not have the resources… Read More

So, Why Not Just Write Better Rules?

In my submission about TSMC making some DFM analysis steps mandatory at 45nm (see “TSMC’s DFM Announcement”), I ended with a question about why the foundries can’t just write better design rules (and rule decks) to make sure all designs yield well. Here’s my take on this complicated question.… Read More

TSMC’s DFM Announcement

If you are a TSMC customer, no doubt you have heard TSMC is requiring lithography and planarity analysis for all 45nm designs. Their website says customers can either run it themselves, or contract TSMC services to do it. The most cost-effective way would be for the customers to run it themselves, but some might not have the resources… Read More

Effects of Inception

I finally got to watch the critically acclaimed sci-fi movie “Inception” last weekend and life has not been the same since. Without giving away too much detail for the benefit of those who have not watched it yet, the main plot involves dreams within dreams within dreams – three levels to be precise—to “incept” an idea into … Read More

Semiconductor Manufacturing International Corporation 2010

In celebrating the 10th anniversary of SMIC, CEO David Wang ushers in a new era of China semiconductor manufacturing with triumphs versus promises. By triumphs David means profits, which SMIC saw for the first time in Q2 2010. The future looks even brighter for SMIC as the China semiconductor demand versus supply gap is an estimated… Read More

Solving the EDA tool fragmentation crisis